Demonstrate how a compiler might translate the following fragment of code into a form that can run

Question:

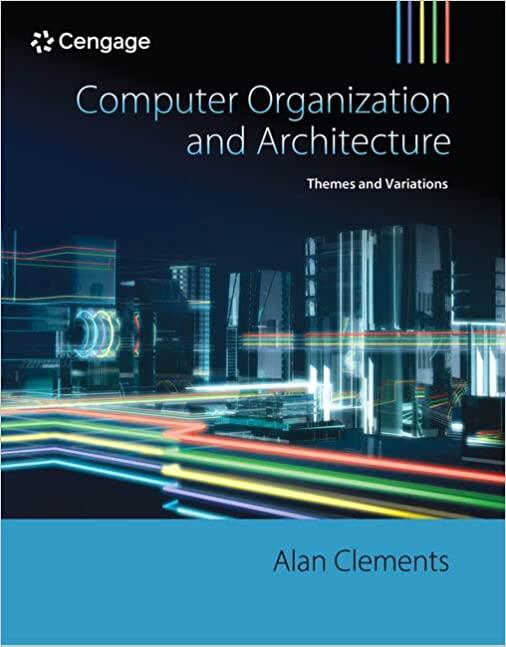

Demonstrate how a compiler might translate the following fragment of code into a form that can run on a VLIW processor that specifies three operations per instruction word (i.e., three instructions per bundle in ltanium terminology). You may perform instruction reordering. Assume that the latency for a load is three cycles and the latency for a multiply is two cycles (i.e., the load takes three cycles in total). Use a NOP whenever an instruction slot cannot be filled.

![MOV 17,#4 LDR r1, [12] LDR r3, [14] LDR r5, [16] ADD rl, rl, r3 ADD rl, rl, r5 DIV rl, rl, r7 ADD r2, #8, r2](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1705/7/6/8/93865abf7ea051cd1705768938548.jpg)

Repeat the same exercise, but assume that the VLIW processor can perform only one memory access operation per cycle. Assume that the memory unit is fully pipelined; that is, it has a latency of three cycles but the next memory operation can begin in the following cycle.

Step by Step Answer:

Computer Organization And Architecture Themes And Variations

ISBN: 9781111987046

1st Edition

Authors: Alan Clements