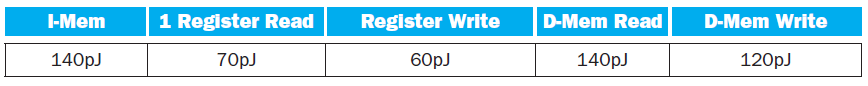

This exercise explores energy efficiency and its relationship with performance. Problems in this exercise assume the following

Question:

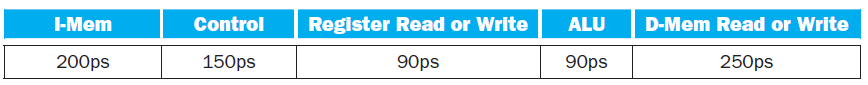

Assume that components in the datapath have the following latencies. You can assume that the other components of the datapath have negligible latencies.

1. How much energy is spent to execute an ADD instruction in a single-cycle design and in the 5-stage pipelined design?

2. What is the worst-case MIPS instruction in terms of energy consumption, and what is the energy spent to execute it?

3. If energy reduction is paramount, how would you change the pipelined design? What is the percentage reduction in the energy spent by an LW instruction aft er this change?

4. What is the performance impact of your changes from 4.19.3?

5. We can eliminate the MemRead control signal and have the data memory be read in every cycle, i.e., we can permanently have MemRead=1. Explain why the processor still functions correctly aft er this change. What is the effect of this change on clock frequency and energy consumption?

Step by Step Answer:

Computer Organization and Design The Hardware Software Interface

ISBN: 978-0124077263

5th edition

Authors: David A. Patterson, John L. Hennessy