The bus system of Fig. 8-2 has the following propagation delay times: 30 ns for the signals

Question:

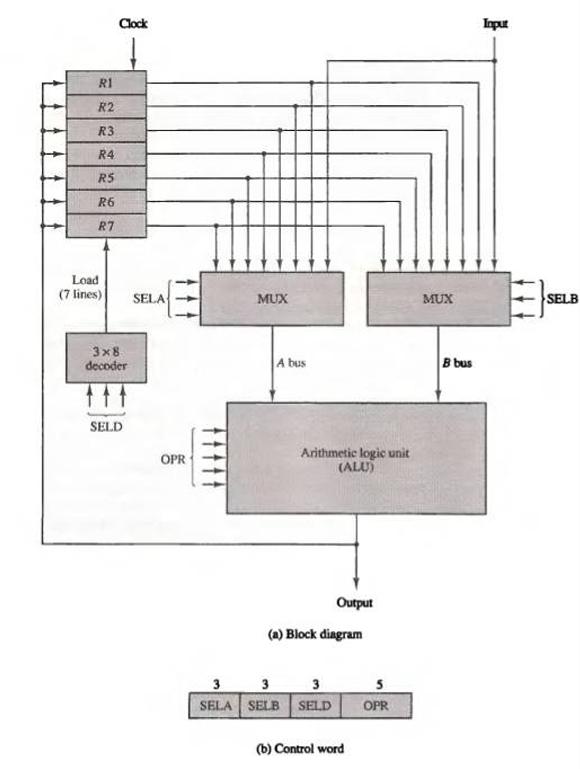

The bus system of Fig. 8-2 has the following propagation delay times: 30 ns for the signals to propagate through the multiplexers, 80 ns to perform the ADD operation in the ALU, 20 ns delay in the destination decoder, and 10 ns to clock the data into the destination register. What is the minimum cycle time that can be used for the clock?

Fig. 8-2

Transcribed Image Text:

R1 R2 R3 R4 R5 R6 R7 Load (7 lines) Clock 3x8 decoder SELD SELA OPR | | | | | MUX A bus Arithmetic logic unit (ALU) Output (a) Block diagram 3 3 3 SELA SELB SELD (b) Control word 5 OPR MUX 8 bus Input SELB

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 100% (2 reviews)

To determine the minimum cycle time for the clock of the bus system we need to consider the sum of t...View the full answer

Answered By

Mario Alvarez

I teach Statistics and Probability for students of my university ( Univerisity Centroamerican Jose Simeon Canas) in my free time and when students ask for me, I prepare and teach students that are in courses of Statistics and Probability. Also I teach students of the University Francisco Gavidia and Universidad of El Salvador that need help in some topics about Statistics, Probability, Math, Calculus. I love teaching Statistics and Probability! Why me?

** I have experience in Statistics and Probability topics for middle school, high school and university.

** I always want to share my knowledge with my students and have a great relationship with them.

** I have experience working with students online.

** I am very patient with my students and highly committed with them

5.00+

1+ Reviews

10+ Question Solved

Related Book For

Question Posted:

Students also viewed these Computer science questions

-

Planning is one of the most important management functions in any business. A front office managers first step in planning should involve determine the departments goals. Planning also includes...

-

The pipeline of Fig. 9-2 has the following propagation times: 40 ns for the operands to be read from memory into registers R1 and R2, 45 ns for the signal to propagate through the multiplier, 5 ns...

-

The state tax department wants to set up what would amount to a series of identical production lines (running 8 hours a day) for processing state tax returns that are submitted on the state's "EZ"...

-

The cylinder in the figure has a radius of 2 ft and rolls without slipping on the horizontal surface. The bar AB is attached to the periphery of the cylinder by a pin at point A. The other end of the...

-

What is the intrinsic value of a put option? How do we interpret this value?

-

Submit a hypothesis development and investigation plan for Waste Management, LLC. Consider potential frauds and perpetrators in your company, how the fraud could be investigated, regulatory issues,...

-

Architecture is defined from two perspectives: the product itself and the development of the product. Compare the two definitions.

-

The unadjusted trial balance of Irvine Inn Company at December 31, 2016, and the data needed for the adjustments follow. Adjustment data at December 31 follow: a. As of December 31, Irvine Inn had...

-

Write a python program that drawing the following fill two circles with colors. Python Turtle Graphics

-

Specify the control word that must be applied to the processor of Fig. 8-2 to implement the following microoperations. a. R1R2 + R3 b. R4R4 c. R5R5 - 1 d. R6input Fig. 8-2 R1 R2 R3 R4 R5 R6 R7 Load...

-

A bus-organized CPU similar to Fig. 8-2 has 16 registers with 32 bits in each, an ALU, and a destination decoder. a. How many multiplexers are there in the A bus, and what is the size of each...

-

As discussed in the text, in the absence of market imperfections and tax effects, we would expect the share price to decline by the amount of the dividend payment when the stock goes ex dividend....

-

Paul Posner argues that many actors and forces have contributed to a shift in the system of intergovernmental relations from "voluntaristic" to "coercive" tools of federal action. What does he mean...

-

If the exchange rate is 10 pesos per Canadian dollar, it is also 0.10 Canadian dollars per peso. Question 4 options: True False

-

Examine the role of DRPI in bringing to light the historical legacy of colonization as a factor in disability outcomes for Canada's First Nations, Indigenous and Mtis peoples. What are the key...

-

Moving forward with the knowledge you have gained from this course, as well as any work experience, what issues do you think will become increasingly important to HRM? Explain your answer. You must...

-

1. The Plastco machine operators appear to be suffering from low job satisfaction and motivation. Why do you think the machine operators are experiencing these problems? 2. Develop options for...

-

Given the following observations from a sample, calculate the mean, the median, and the mode. 12 12 10

-

For liquid water the isothermal compressibility is given by; where r and b are functions of temperature only. If 1 kg of water is compressed isothermally and reversibly from I to 500 bar at 60(C. how...

-

Write down the binary representation of the decimal number 63.25 assuming the IEEE 754 double precision format.

-

Write down the binary representation of the decimal number 63.25 assuming it was stored using the single precision IBM format (base 16, instead of base 2, with 7 bits of exponent).

-

Write down the binary bit pattern to represent -1.5625 10 -1 assuming a format similar to that employed by the DEC PDP-8 (the left most 12 bits are the exponent stored as a twos complement number,...

-

Assume your firm has transferred you to Zurich Switzerland. You work in the triangular arbitrage division. View the following exchange rates. Is an arbitrage opportunity available? If not,= explain...

-

International Bond has a Macaulay Duration of 6.0, modified duration of 6.5, and Convexity of 50.25. If the bond's yield to maturity decreases by 50 bps, how much will be the expected percentage...

-

A newly issued International annual-pay coupon bond has the following characteristics: Trading at par (100 CHF). Time to maturity of 15 years Coupon rate of 9.5% Based on an 85-basis-point increase...

Study smarter with the SolutionInn App