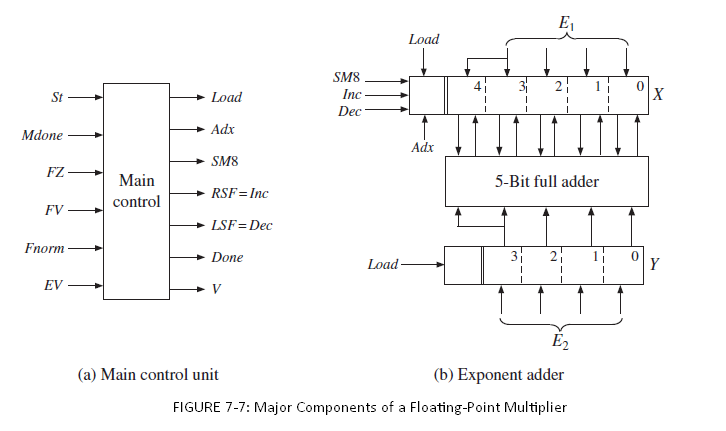

Redesign the floating-point multiplier in Figure 7. 7 using a common 5-bit full adder connected to a

Question:

(a) Redraw the block diagram, being sure to include the connections to the bus, and include all control signals.

(b) Draw a new SM chart for the new control.

(c) Write the Verilog description for the multiplier or specify the changes that need to be made to an existing description.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: