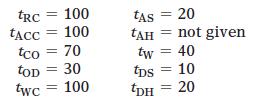

A certain static RAM has the following timing parameters (in nanoseconds): (a) How long after the address

Question:

A certain static RAM has the following timing parameters (in nanoseconds):

(a) How long after the address lines stabilize will valid data appear at the outputs during a read cycle?

(b) How long will output data remain valid after C̅S̅ returns HIGH?

(c) How many read operations can be performed per second?

(d) How long should WE and C̅S̅ be kept HIGH after the new address stabilizes during a write cycle?

(e) What is the minimum time that input data must remain valid for a reliable write operation to occur?

(f) How long must the address inputs remain stable after W̅E̅ and C̅S̅ return HIGH?

(g) How many write operations can be performed per second?

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Principles And Application

ISBN: 9780134220130

12th Edition

Authors: Ronald Tocci, Neal Widmer, Gregory Moss

Question Posted: