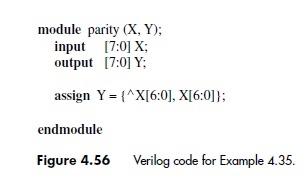

Example 4.35 and Figure 4.56 show how a circuit that generates an ASCII byte suitable for sending

Question:

Example 4.35 and Figure 4.56 show how a circuit that generates an ASCII byte suitable for sending over a communications link may be defined. Write Verilog code for its counterpart at the receiving end, where byte Y (which includes the parity bit) has to be converted into byte X in which the bit x7 has to be 0. An error signal has to be produced, which is set to 0 or 1 depending on whether the parity check indicates correct or erroneous transmission, respectively.

Transcribed Image Text:

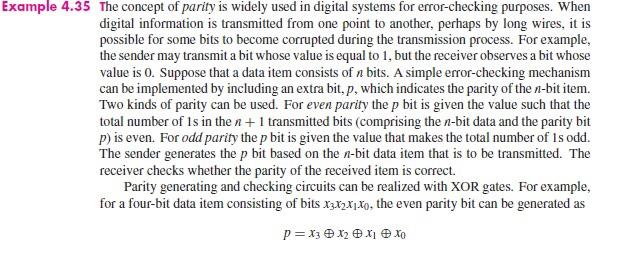

Example 4.35 The concept of parity is widely used in digital systems for error-checking purposes. When digital information is transmitted from one point to another, perhaps by long wires, it is possible for some bits to become corrupted during the transmission process. For example, the sender may transmit a bit whose value is equal to 1, but the receiver observes a bit whose value is 0. Suppose that a data item consists of a bits. A simple error-checking mechanism can be implemented by including an extra bit, p, which indicates the parity of the n-bit item. Two kinds of parity can be used. For even parity the p bit is given the value such that the total number of 1s in the n + 1 transmitted bits (comprising the n-bit data and the parity bit p) is even. For odd parity the p bit is given the value that makes the total number of 1s odd. The sender generates the p bit based on the n-bit data item that is to be transmitted. The receiver checks whether the parity of the received item is correct. Parity generating and checking circuits can be realized with XOR gates. For example, for a four-bit data item consisting of bits x3x₂x₁x, the even parity bit can be generated as P = X3 X₂X1 X

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 75% (12 reviews)

Here is the Verilog code for the receiver end of the circuit described in Example 435 and Figur...View the full answer

Answered By

James Warinda

Hi! I’m James Otieno and I'm an experienced professional online tutor with countless hours of success in tutoring many subjects in different disciplines. Specifically, I have handled general management and general business as a tutor in Chegg, Help in Homework and Trans tutor accounts.

I believe that my experience has made me the perfect tutor for students of all ages, so I'm confident I can help you too with finding the solution to your problems. In addition, my approach is compatible with most educational methods and philosophies which means it will be easy for you to find a way in which we can work on things together. In addition, my long experience in the educational field has allowed me to develop a unique approach that is both productive and enjoyable.

I have tutored in course hero for quite some time and was among the top tutors awarded having high helpful rates and reviews. In addition, I have also been lucky enough to be nominated a finalist for the 2nd annual course hero award and the best tutor of the month in may 2022.

I will make sure that any student of yours will have an amazing time at learning with me, because I really care about helping people achieve their goals so if you don't have any worries or concerns whatsoever you should place your trust on me and let me help you get every single thing that you're looking for and more.

In my experience, I have observed that students tend to reach their potential in academics very easily when they are tutored by someone who is extremely dedicated to their academic career not just as a businessman but as a human being in general.

I have successfully tutored many students from different grades and from all sorts of backgrounds, so I'm confident I can help anyone find the solution to their problems and achieve

0.00

0 Reviews

10+ Question Solved

Related Book For

Fundamentals Of Digital Logic With Verilog Design

ISBN: 9780073380544

3rd Edition

Authors: Stephen Brown, Zvonko Vranesic

Question Posted:

Students also viewed these Computer science questions

-

Design a circuit that generates the 9s complement of a BCD digit.

-

Write a program that receives an ASCII code (an integer between 0 and 127) and displays its character. For example, if the user enters 97, the program displays the character a. Here is a sample run:...

-

Write Verilog code for the boundary scan cell of Figure 10-14(b). Rewrite the Verilog code of Figure 10-21 to use this boundary scan cell as a component in place of some of the behavioral code for...

-

Figlio (1999) found that legislators are more likely to mirror their constituents preferences during election years than in earlier years of their terms. This is particularly true for relatively...

-

To figure out if Yahoos telecommuting is less productive than it should have been Mayer looked at the log of Yahoos Virtual Private Network to see how frequently employees checked in. What do you...

-

Kazz Industries year-end is May 31. Based on an analysis of the unadjusted trial balance at May 31, 2020, the following information was available: a. Machinery costing $77,500 was acquired on...

-

Indicate the three questions that are of concern in performing compliance tests and the auditing procedures used in these tests.

-

Top managers of CC Oliver Products, Inc., have asked for your help in comparing the companys profit performance and financial position with the average for the industry. The accountant has given you...

-

1. What is the independent variable in the study? Why? 2. What is the dependent variable in the study? Why? 3. How could this information be useful to emergency managers/emergency planners? 4. Do you...

-

Air travel on Mountain Airlines for the past 18 weeks was: b. Use an appropriate technique to develop a forecast for the expected number of passengers for the next three weeks. (Round your...

-

The spectral distribution of the radiation emitted by a diffuse surface may be approximated as follows. (a) What is the total emissive power? (b) What is the total intensity of the radiation emitted...

-

Write Verilog code that implements the task in Problem 4.30. Data From Problem 4.30 Design a circuit that can multiply an eight-bit number, A = a 7 , . . . , a 0 , by 1, 2, 3 or 4 to produce the...

-

Which federal law is concerned with child labor, minimum wages, and overtime?

-

Write a sub-query that returns all orders placed on the last day of activity that can be found in the Orders table. Include the orderid, orderdate, customerid, and the employeeid. #2: SUB-QUERY -...

-

Every home football game for the past 8 years at Southwestern University has been sold out. The revenues from ticket sales are significant, but the sale of food, beverages, and souvenirs has...

-

Public financial management ( PFM ) has been narrowly defined to cover the budget cycle, which typically centers around ( 1 ) budget formulation; ( 2 ) budget execution; ( 3 ) accounting and...

-

On 1 5 October 2 0 1 9 , the board of directors of MAA Bhd decided to close down one of its overseas divisions due to continuous losses. For this reason, a detailed plan was drafted and all costs...

-

Lusanda. When the parties married, Sipho had no assets apart from his interest in his pension fund, valued at R50 000. He had started a new business and had an outstanding loan of R100 000. Lusanda...

-

What are the advantages of using the concepts of stress and strain to describe deformations?

-

Hardin Services Co. experienced the following events in 2016: 1. Provided services on account. 2. Collected cash for accounts receivable. 3. Attempted to collect an account and, when unsuccessful,...

-

Suppose that two different types of sources are used in a term paper: books and journal articles. The following UML diagram illustrates how the sources are organized. First, implement the three...

-

Write a class Vehicle which keeps a vehicle identification number, license plate number, and a number of axles. Derive two classes from the Vehicle class named Car and Truck. Include a data member...

-

Implement a class Engineer which extends from the FullTime class discussed in Sect. 9.5. Include a data member which describes the type of engineering and a method tostring.

-

Assignment: Email Your Instructor Instructions: Planning < > Read the document, Professional Email for D2L, to understand the etiquette and layout for this email. This is SharePoint file. If you...

-

Find the entry for Customer number: 216582, Region: East, Date of sale: 1/1/2015, Brand: Jeffrey Alexander, Collection: Torino, Description: 3" CC pull, List price: $2.52, Quantity 380. What is the...

-

H Week Four Discussion Post a response to this prompt on the discussion board: 1. Which part of the essay (introduction paragraph, thesis statement, body paragraphs, topic sentences, conclusion...

Study smarter with the SolutionInn App