1. Design a synchronous up-down counter that has the following up and down sequences: (0, 1,...

Fantastic news! We've Found the answer you've been seeking!

Question:

Transcribed Image Text:

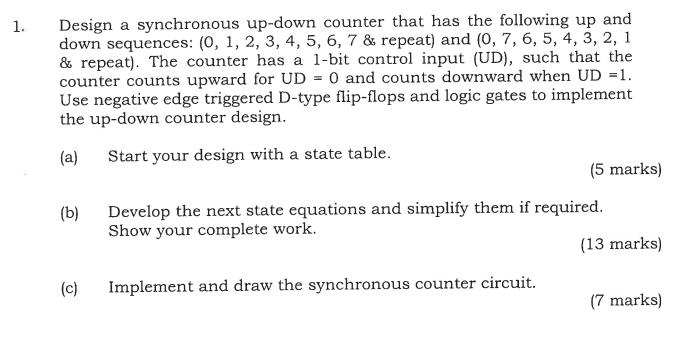

1. Design a synchronous up-down counter that has the following up and down sequences: (0, 1, 2, 3, 4, 5, 6, 7 & repeat) and (0, 7, 6, 5, 4, 3, 2, 1 & repeat). The counter has a 1-bit control input (UD), such that the counter counts upward for UD = 0 and counts downward when UD 1. Use negative edge triggered D-type flip-flops and logic gates to implement the up-down counter design. (a) Start your design with a state table. (b) (c) (5 marks) Develop the next state equations and simplify them if required. Show your complete work. Implement and draw the synchronous counter circuit. (13 marks) (7 marks) 1. Design a synchronous up-down counter that has the following up and down sequences: (0, 1, 2, 3, 4, 5, 6, 7 & repeat) and (0, 7, 6, 5, 4, 3, 2, 1 & repeat). The counter has a 1-bit control input (UD), such that the counter counts upward for UD = 0 and counts downward when UD 1. Use negative edge triggered D-type flip-flops and logic gates to implement the up-down counter design. (a) Start your design with a state table. (b) (c) (5 marks) Develop the next state equations and simplify them if required. Show your complete work. Implement and draw the synchronous counter circuit. (13 marks) (7 marks) 1. Design a synchronous up-down counter that has the following up and down sequences: (0, 1, 2, 3, 4, 5, 6, 7 & repeat) and (0, 7, 6, 5, 4, 3, 2, 1 & repeat). The counter has a 1-bit control input (UD), such that the counter counts upward for UD = 0 and counts downward when UD 1. Use negative edge triggered D-type flip-flops and logic gates to implement the up-down counter design. (a) Start your design with a state table. (b) (c) (5 marks) Develop the next state equations and simplify them if required. Show your complete work. Implement and draw the synchronous counter circuit. (13 marks) (7 marks) 1. Design a synchronous up-down counter that has the following up and down sequences: (0, 1, 2, 3, 4, 5, 6, 7 & repeat) and (0, 7, 6, 5, 4, 3, 2, 1 & repeat). The counter has a 1-bit control input (UD), such that the counter counts upward for UD = 0 and counts downward when UD 1. Use negative edge triggered D-type flip-flops and logic gates to implement the up-down counter design. (a) Start your design with a state table. (b) (c) (5 marks) Develop the next state equations and simplify them if required. Show your complete work. Implement and draw the synchronous counter circuit. (13 marks) (7 marks)

Expert Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Posted Date:

Students also viewed these computer network questions

-

You are asked to develop a Floppy Disk program that allows users to access a floppy disk locally mounted on a computer. You are expected to use C programming language. In your program, all file I/O...

-

Torque RPM 1. HP = Solve this equation for RPM. 5252 2. When presented with an equation with fractional coefficients what should be your first step? 3. Solve this equation for w. 3(w + y) + 2 = k 4....

-

Adjustable-Rate and Subprime Mortgages The term subprime mortgage refers to mortgages given to home buyers with a heightened perceived risk of default, when, for instance, the price of the home being...

-

A box is 4 in. high. Its length is I.5 times its width. The volume of the box is 1350 in. 2 . What are the width and length of the box? 2 answers

-

Suppose that initially the data in Problem 24-17 apply, but then an increase in fixed costs occurs. As a result, the ATC curve in Figure 24-6 shifts upward, As a result, the average total cost of...

-

Suppose you wish to determine if the mean IQ of students on your campus is different from the mean IQ in the general population, 100. To conduct this study, you obtain a simple random sample of 50...

-

How would you defi ne the difference between a responsible board and an exceptional board?

-

The widget market is competitive and includes no transaction costs. Five suppliers are willing to sell one widget at the following prices: $30, $29, $20, $16, and $12. Five buyers are willing to buy...

-

g Excel, submit the following: i. Calculate Rashmika's minimum net income for tax purposes in accordance with the ordering provisions found in section 3 of the Income Tax Act, and her minimum taxable...

-

The Bayview Resort has three operating departmentsthe Convention Center, Food Services, and Guest Lodgingthat are supported by three service departments General Administration, Cost Accounting, and...

-

1) Exhibit 13-4 In a completely randomized experimental design involving five treatments, 13 observations were recorded for each of the five treatments. The following information is provided. SSTR =...

-

What are the gears used for intersecting shafts?

-

What is control risk? How does the auditor assess control risk on an engagement? How are the concepts of inherent risk and control risk related?

-

What do you mean by static and dynamic balance of machinery

-

A thorough understanding of the business and the risks facing the business will help the auditor assess all of the following except: a. Significant accounting estimates (e.g., warranty liabilities or...

-

What do you mean by primary and secondary unbalance in reciprocating engines?

-

In 2024, Cici, a physician who is 55 years old, brought in $200,000 before taxes. In ten years, she intends to leave her current position to launch her own company. Cici plans to open new TFSA, RRSP,...

-

Match the following. Answers may be used more than once: Measurement Method A. Amortized cost B. Equity method C. Acquisition method and consolidation D. Fair value method Reporting Method 1. Less...

-

Construct an SM chart that is equivalent to the following state table. Test only one variable in each decision box. Try to minimize the number of decision boxes. Show Mealy and Moore outputs on the...

-

(a) Implement an 8-to-1 multiplexer using a minimum number of logic blocks of the type shown in Figure 6-1(a). Give the X and Y functions for each block and show the connections between blocks. (b)...

-

Make any necessary changes in the Verilog code for the traffic light controller so that it can be synthesized without latches using whatever synthesis tool you have available. Synthesize the code...

-

The vertices in the graph below are grain elevators, some of which can be connected by chutes to neighboring elevators, for the purpose of shifting grain from one location to another. The edges are...

-

An alternative algorithm for finding the shortest path from the root \(v_{0}\) to each vertex \(v\) in a directed graph, called Dijkstra's algorithm, is as follows. Initialize the cost \(C(v)\) of a...

-

Use Dijkstra's algorithm (see Exercise 14) to list shortest paths to all vertices \(v_{1}, \ldots, v_{7}\) in the graph of Exercise 11 Do this by hand, rather than with Mathematica.

Study smarter with the SolutionInn App