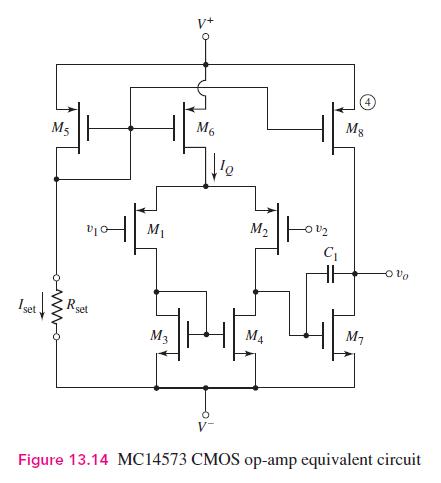

The CMOS op-amp in Figure 13.14 is biased at (V^{+}=5 mathrm{~V}) and (V^{-}=) (-5 mathrm{~V}). Let (R_{mathrm{set}}=50

Question:

The CMOS op-amp in Figure 13.14 is biased at \(V^{+}=5 \mathrm{~V}\) and \(V^{-}=\) \(-5 \mathrm{~V}\). Let \(R_{\mathrm{set}}=50 \mathrm{k} \Omega\). Assume transistor parameters of \(V_{T N}=0.7 \mathrm{~V}\), \(V_{T P}=-0.7 \mathrm{~V}, k_{n}^{\prime}=100 \mu \mathrm{A} / \mathrm{V}^{2}, k_{p}^{\prime}=40 \mu \mathrm{A} / \mathrm{V}^{2}, \lambda_{n}=0.02 \mathrm{~V}^{-1}\), and \(\lambda_{p}=0.04 \mathrm{~V}^{-1}\). The transistor width-to-length ratios are \((W / L)_{3,4}=15\), \((W / L)_{7}=30\), and \((W / L)=50\) for all other transistors.

(a) Determine \(I_{\text {set }}\), \(I_{Q}\), and \(I_{D Q 7}\).

(b) Find the small-signal voltage gains of the input and second stages, and the overall voltage gain.

Step by Step Answer:

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen