Given Z(T, U, V, W, X, Y) = VW'X + U'V'WY + TV'WY', (a) Show how Z

Question:

Given Z(T, U, V, W, X, Y) = VW'X + U'V'WY + TV'WY',

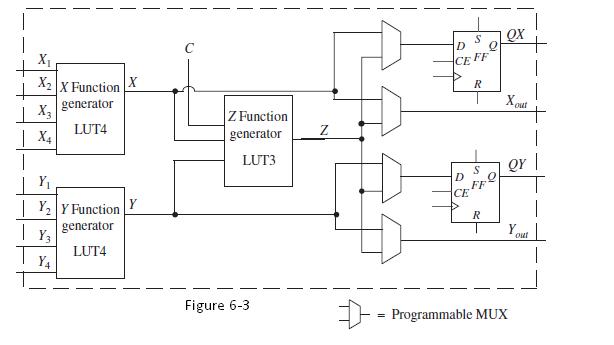

(a) Show how Z can be realized using a single Figure 6-3 logic block. Show the cell inputs on a copy of Figure 6-3; indicate the internal connections in the cell; and specify the functions X, Y, and Z.

Figure 6-3

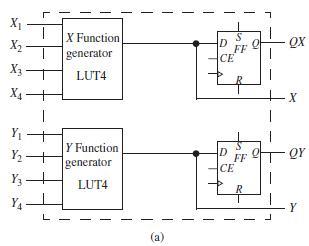

(b) Show how Z can be realized using two Figure 6-1(a) logic blocks. Draw a diagram showing the inputs to each cell, the interconnections between cells, and the X and Y functions for each cell.

Figure 6-1(a)

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: