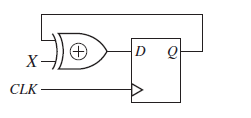

In the following circuit, the XOR gate has a delay in the range of 2 to 16

Question:

(a) What is the minimum clock period for proper operation of the circuit?

(b) What are the earliest and latest times after the rising clock edge at which X is allowed to change and still have proper synchronous operation? (Assume minimum clock period from (a).)

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: