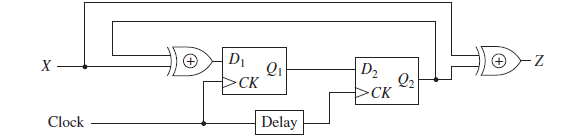

In the following circuit, the XOR gate has a delay in the range of 2 to 16

Question:

time is 8 ns, and the hold time is 4 ns.

(a) Assume delay = 0 ns and compute the maximum frequency at which this circuit can be safely clocked.

(b) Assume delay = 5 ns and compute the maximum frequency at which this circuit can be safely clocked.

(c) Assume delay = €“5 ns (i.e., the first flip gets the clock delayed 5 ns as compared with the second flip-flop) and compute the maximum frequency at which this circuit can be safely clocked.

(d) Assume delay = 0 ns and compute the earliest time and latest times after or before the rising clock edge that X is allowed to change and still have proper synchronous operation?

(e) Assume delay = 5 ns and compute the earliest time and latest times after or before the rising clock edge at which X is allowed to change and still have proper synchronous operation?

(f) Assume delay = €“5 ns and compute the earliest time and latest times after or before the rising clock edge at which X is allowed to change and still have proper synchronous operation?

Step by Step Answer:

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee