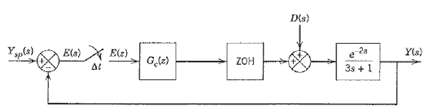

The block diagram of a digital control system is shown in Fig. The sampling period is ?t

Question:

The block diagram of a digital control system is shown in Fig. The sampling period is ?t 1 min.(a) Design the digital controller Gc(z) so that the closed-loop system exhibits a first-order response to a unit step change in the set point (after an appropriate lime delay).(b) Will this controller eliminate offset after a step change in the set point? Justify your answer.(c) Is the controller physically realizable? Justify your answer.(d) Design a digital PID controller based on the ITAE (set-point) method in Chapter 12 and examine its performance for a step change in set point. Approximate the sampler and zero-order- hold by a time delay of ? ?t/2.

Step by Step Answer:

Process Dynamics And Control

ISBN: 978-0471000778

2nd Edition

Authors: Dale E. Seborg, Thomas F. Edgar, Duncan A. Mellich