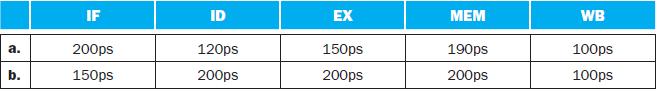

Given these pipeline stage latencies, repeat the speedup calculation from 4.14.2, but take into account the (possible)

Question:

Given these pipeline stage latencies, repeat the speedup calculation from 4.14.2, but take into account the (possible) change in clock cycle time. When EX and MEM are done in a single stage, most of their work can be done in parallel. As a result, the resulting EX/MEM stage has a latency that is the larger of the original two, plus 20ps needed for the work that could not be done in parallel.

Problem 4.14.2

For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we change load/store instructions to use a register (without an offset) as the address, these instructions no longer need to use the ALU. As a result, MEM and EX stages can be overlapped and the pipeline has only 4 stages. Change this code to accommodate this changed ISA. Assuming this change does not affect clock cycle time, what speedup is achieved in this instruction sequence?

The remaining problems in this exercise assume that individual pipeline stages have the following latencies:

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy