Suppose we could take the system of Figure 4.32 and divide it into an arbitrary number of

Question:

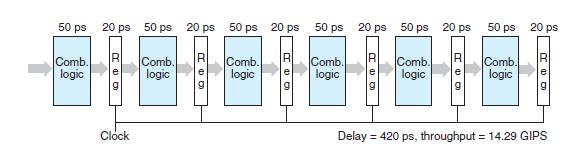

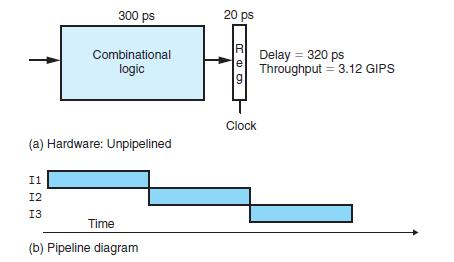

Suppose we could take the system of Figure 4.32 and divide it into an arbitrary number of pipeline stages k, each having a delay of 300/k, and with each pipeline register having a delay of 20 ps.

A. What would be the latency and the throughput of the system, as functions of k?

B. What would be the ultimate limit on the throughput?

Figure 4.32

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Computer Systems A Programmers Perspective

ISBN: 9781292101767

3rd Global Edition

Authors: Randal E. Bryant, David R. O'Hallaron

Question Posted: