Design a ternary full-adder circuit, using the approach described in Problem 3.25. Data From Problem 3.25 In

Question:

Design a ternary full-adder circuit, using the approach described in Problem 3.25.

Data From Problem 3.25

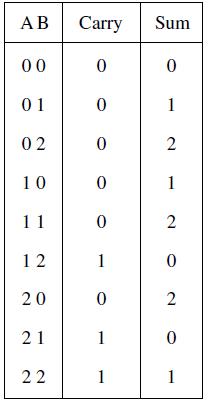

In a ternary number system there are three digits: 0, 1, and 2. Figure P3.3 defines a ternary half-adder. Design a circuit that implements this half-adder using binary-encoded signals, such that two bits are used for each ternary digit. Let A = a1a0, B = b1b0, and Sum = s1s0; Carry is just a binary signal. Use the following encoding: 00 = (0)3, 01 = (1)3, and 10 = (2)3. Minimize the cost of the circuit.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Fundamentals Of Digital Logic With Verilog Design

ISBN: 9780073380544

3rd Edition

Authors: Stephen Brown, Zvonko Vranesic

Question Posted: