Using Figure 3-49 as a guide and a when-else on S from Figure 3-29, write a high-level

Question:

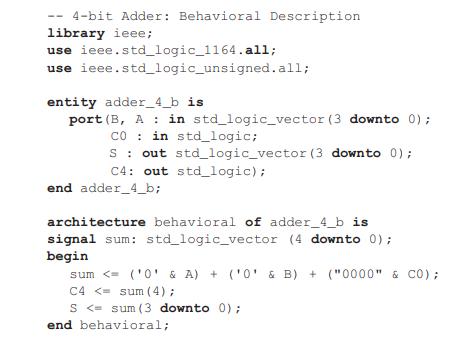

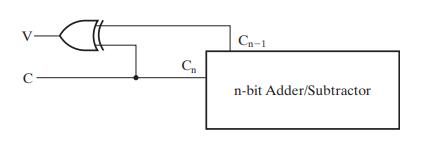

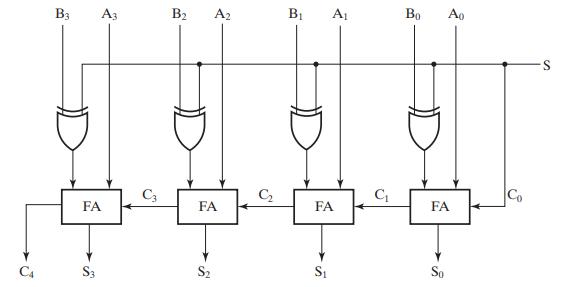

Using Figure 3-49 as a guide and a “when-else” on S from Figure 3-29, write a high-level behavior VHDL description for the adder–subtractor in Figure 3-46 (see Figure 3-45 for details). Compile and simulate your description.

Assuming a ripple carry implementation, apply combinations that check out one of the full adder–subtractor stages for all 16 possible input combinations. Also, apply combinations to check the carry chain connections in between the full adders by demonstrating that a 0 and a 1 can be propagated from C0 to C4. Check the overflow signals as well.

Figure 3-49

Figure 3-46

Figure 3-45

Figure 3-45

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin

Question Posted: