Write a gate- level HDL description of the circuit from Problem 4-59 including delays for each component.

Question:

Write a gate- level HDL description of the circuit from Problem 4-59 including delays for each component. Show that the circuit operates incorrectly when operated at a frequency greater than the maximum frequency you found as your answer for Problem 4-59.

Problem 4-59

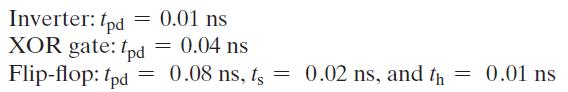

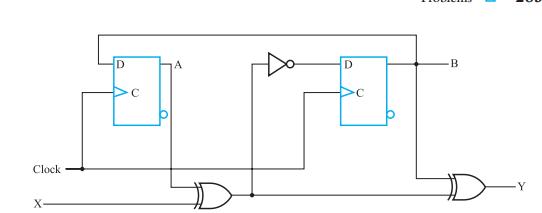

A sequential circuit is shown in Figure 4-49. The timing parameters for the gates and lip- lops are as follows:

Figure 4-49:

(a) Find the longest path delay from an external circuit input passing through gates only to an external circuit output.

b) Find the longest path delay in the circuit from an external input to positive clock edge.

(c) Find the longest path delay from positive clock edge to output.

(d) Find the longest path delay from positive clock edge to positive clock edge.

(e) Determine the maximum frequency of operation of the circuit in megahertz (MHz).

Step by Step Answer:

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin