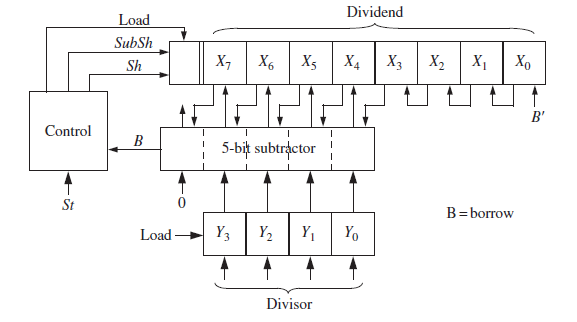

A block diagram for a divider that divides an 8-bit unsigned number by a 4-bit unsigned number

Question:

(a) Draw a state graph for the controller (five states).

(b) Complete the Verilog code that follows. Registers and signals should be of type unsigned so that overloaded operators may be used. Write behavioral code that uses a single always block.

module divu(dividend, divisor, St, clk, quotient);

input[7:0] dividend;

input[3:0] divisor;

input St,clk;

output[3:0] quotient;

.

.

.

endmodule

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: