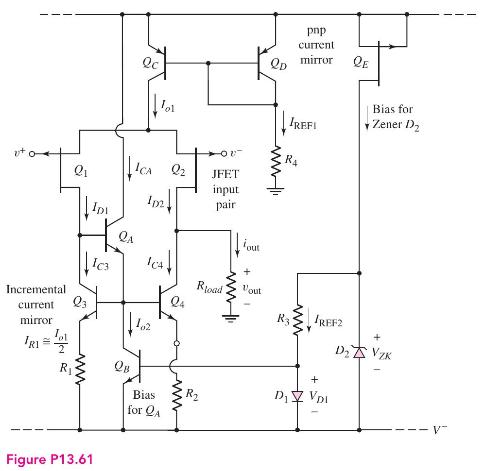

Consider the BiFET differential input stage in Figure P13.61, biased with power supply voltages (V^{+})and (V^{-}). Let

Question:

Consider the BiFET differential input stage in Figure P13.61, biased with power supply voltages \(V^{+}\)and \(V^{-}\). Let \(V^{+}=-V^{-} \equiv V_{S}\).

(a) Design the bias circuit such that \(I_{\mathrm{REF} 2}=100 \mu \mathrm{A}\) for supply voltages in the range \(3 \leq V_{S} \leq 12 \mathrm{~V}\). Determine \(V_{Z K}, R_{3}\), and the JFET parameters.

(b) Determine the value of \(R_{4}\) such that \(I_{O 1}=500 \mu \mathrm{A}\) when \(V^{+}=12 \mathrm{~V}\).

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: