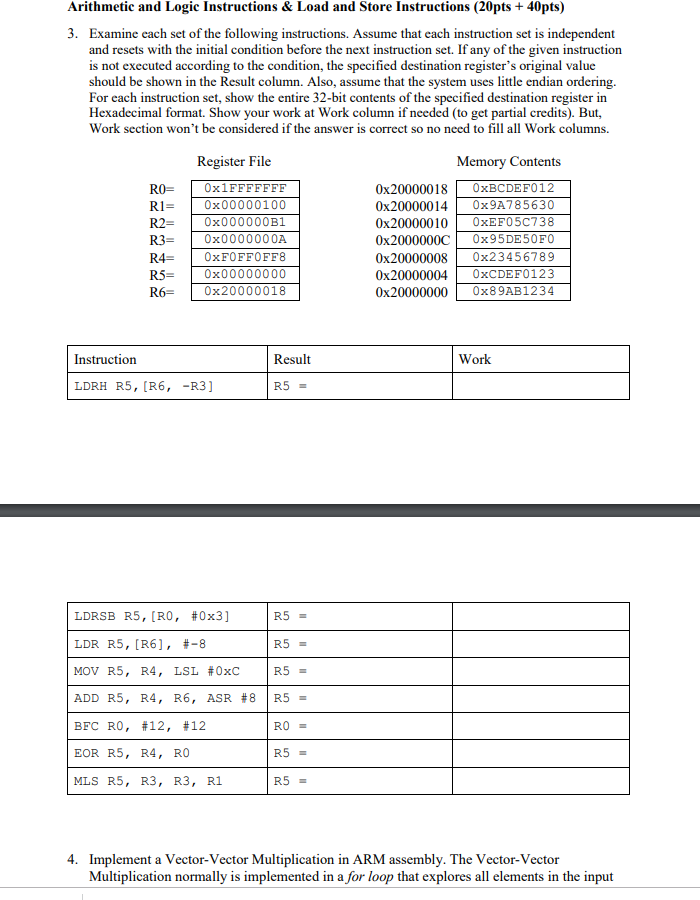

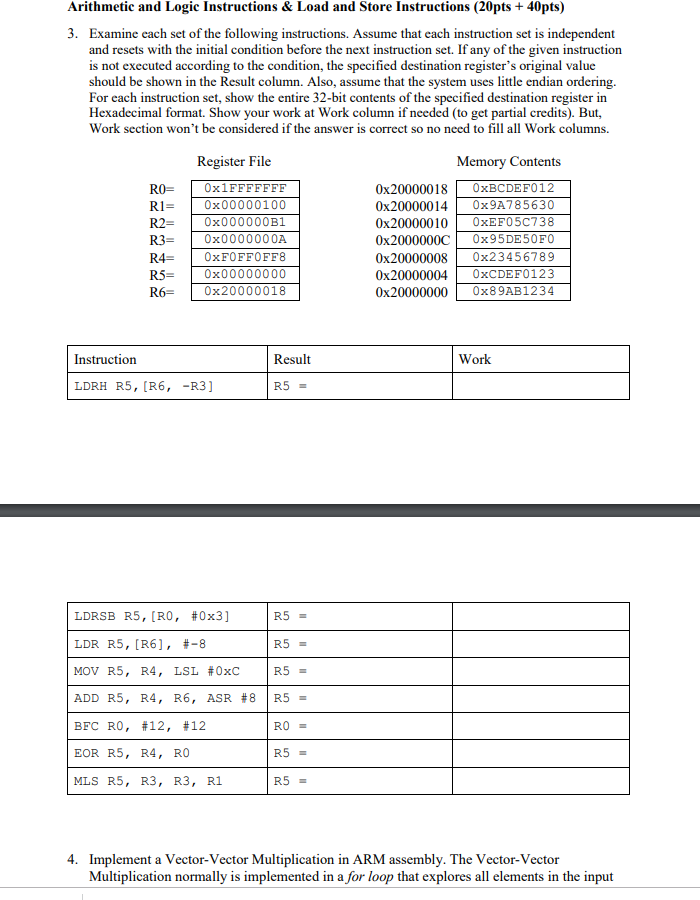

Question: Arithmetic and Logic Instructions& Load and Store Instructions (20pts 40pts) 3. Examine each set of the following instructions. Assume that each instruction set is independent

Arithmetic and Logic Instructions& Load and Store Instructions (20pts 40pts) 3. Examine each set of the following instructions. Assume that each instruction set is independent and resets with the initial condition before the next instruction set. If any of the given instruction is not executed according to the condition, the specified destination register's original value should be shown in the Result column. Also, assume that the system uses little endian ordering For each instruction set, show the entire 32-bit contents of the specified destination register in Hexadecimal format. Show your work at Work column if needed (to get partial credits). But, Work section won't be considered if the answer is correct so no need to fill all Work columns. Register File Memory Contents RO x1FFFFFFF R1-0x00000100 R2-0x000000B1 R30x0000000A R4-0xFOFFOFF8 R5-0x00000000 R6-1 0x20000 L8 0x20000018 0xBCDEF012 0x20000014 0x9A785630 0x20000010 0xEF05C738 0x2000000C 0x95DE50FO 0x20000008 0x23456789 0x20000004 0xCDEF0123 0x20000000 0x89AB1234 Instruction Result Work LDRH R5, [R6, -R3] R5 = LDRSBR5, [R0 , #0x3] LDR R5, [R6], #-8 MOV R5, R4, LSL #OXC ADD R5, R4, R6, ASR #8 | R5 = BFC R0, #12, #12 EOR R5, R4, RO MLS R5, R3, R3, R1 R5 = R5 = R5 - R5 = R5 - 4. Implement a Vector-Vector Multiplication in ARM assembly. The Vector-Vector Multiplication normally is implemented in a for loop that explores all elements in the input Arithmetic and Logic Instructions& Load and Store Instructions (20pts 40pts) 3. Examine each set of the following instructions. Assume that each instruction set is independent and resets with the initial condition before the next instruction set. If any of the given instruction is not executed according to the condition, the specified destination register's original value should be shown in the Result column. Also, assume that the system uses little endian ordering For each instruction set, show the entire 32-bit contents of the specified destination register in Hexadecimal format. Show your work at Work column if needed (to get partial credits). But, Work section won't be considered if the answer is correct so no need to fill all Work columns. Register File Memory Contents RO x1FFFFFFF R1-0x00000100 R2-0x000000B1 R30x0000000A R4-0xFOFFOFF8 R5-0x00000000 R6-1 0x20000 L8 0x20000018 0xBCDEF012 0x20000014 0x9A785630 0x20000010 0xEF05C738 0x2000000C 0x95DE50FO 0x20000008 0x23456789 0x20000004 0xCDEF0123 0x20000000 0x89AB1234 Instruction Result Work LDRH R5, [R6, -R3] R5 = LDRSBR5, [R0 , #0x3] LDR R5, [R6], #-8 MOV R5, R4, LSL #OXC ADD R5, R4, R6, ASR #8 | R5 = BFC R0, #12, #12 EOR R5, R4, RO MLS R5, R3, R3, R1 R5 = R5 = R5 - R5 = R5 - 4. Implement a Vector-Vector Multiplication in ARM assembly. The Vector-Vector Multiplication normally is implemented in a for loop that explores all elements in the input