Question: Consider the circuit below, CD wo 80 w1 82 w8 81 w2 84 w3 w4 87 88 w7 85 Using gate primitives, create a

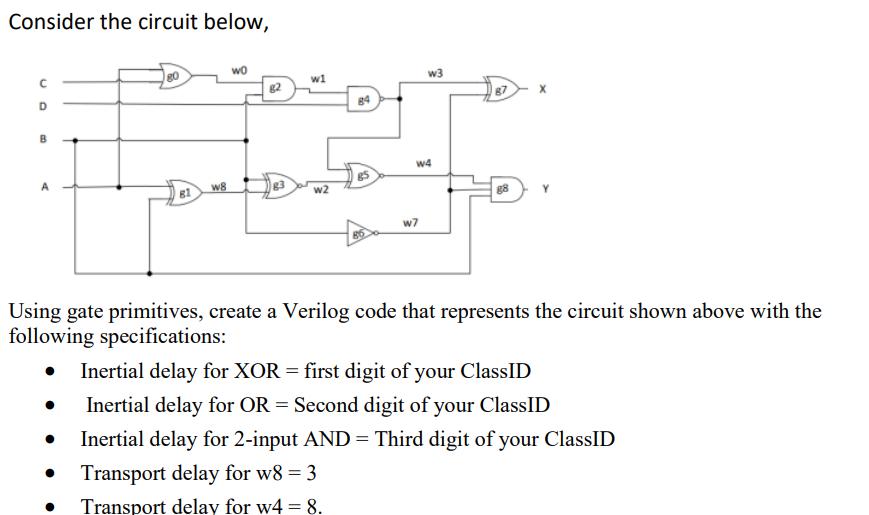

Consider the circuit below, CD wo 80 w1 82 w8 81 w2 84 w3 w4 87 88 w7 85 Using gate primitives, create a Verilog code that represents the circuit shown above with the following specifications: Inertial delay for XOR = first digit of your ClassID Inertial delay for OR = Second digit of your ClassID Inertial delay for 2-input AND = Third digit of your ClassID Transport delay for w8 = 3 Transport delay for w4 = 8.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts