Question: Arithmetic overflow occurs during a two's complement addition if the result of adding two positive numbers yields a negative result or if adding two negative

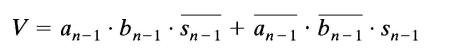

Arithmetic overflow occurs during a two's complement addition if the result of adding two positive numbers yields a negative result or if adding two negative numbers yields a positive result. If the sign bits of A and B are the same but the sign bit of the result is different, arithmetic overflow has occurred. If an-I is the sign bit of A, bn-t is the sign bit of B, and Sn-I is the sign bit of the sum of A and B, then overflow is defined by

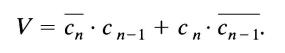

In practice, real systems detect overflow from Cin ≠ ft Cout to the last stage. That is, we detect overflow from

Demonstrate that this expression is correct.

. V = an-1 bn-1 Sn-1+ an-1 bn-1 Sn-1 '

Step by Step Solution

3.26 Rating (152 Votes )

There are 3 Steps involved in it

The diagram illustrates the mostsignificant stage of a parallel adder that adds together bits a n1 b ... View full answer

Get step-by-step solutions from verified subject matter experts