Question: In problem 5.9, it was assumed that all transactions on the system were serially executed, which is both unrealistic and inefficient in a DSM multicore.

In problem 5.9, it was assumed that all transactions on the system were serially executed, which is both unrealistic and inefficient in a DSM multicore.

We now relax this condition. We will require only that all transactions originating in one core are serialized. However, different cores can independently issue their read/write transactions and even compete for the same memory block.

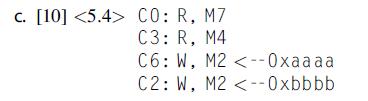

The transactions of problem 5.9 are represented next to reflect the new, relaxed constraints. Redo problem 5.9 with the new, relaxed constraints.

Problem 5.9

For each part of this exercise, assume that initially all caches lines are invalid, and the data in memory Mi is the byte i (0X00 For each of the following parts,

■ Show the final state (i.e., coherence state, sharers/owners, tags, and data) of the caches and directory controller (including data values) after the given transaction sequence has completed;

■ Show the messages transferred (choose a suitable format for message types).

![a. [10] C3: R, M4. C3: R, M2 C7: W, M4](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1706/5/1/6/75465b76112efe561706516754428.jpg)

a. [10] C3: R, M4. C3: R, M2 C7: W, M4

Step by Step Solution

3.24 Rating (148 Votes )

There are 3 Steps involved in it

The problem youve described pertains to cache coherence in a Distributed Shared Memory DSM multicore system which is a complex topic in computer architecture Cache coherence ensures that multiple cach... View full answer

Get step-by-step solutions from verified subject matter experts