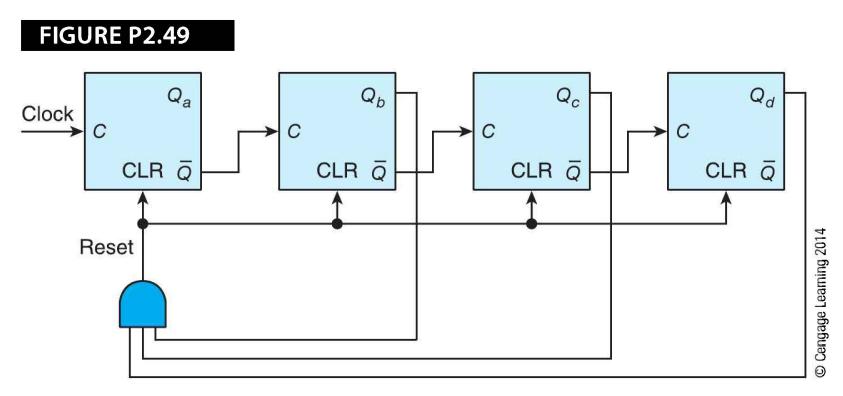

The circuit in Figure P2.49 consists of four JK flip-flops. Inputs J and K are not shown,

Question:

The circuit in Figure P2.49 consists of four JK flip-flops. Inputs J and K are not shown, because it is assumed that they are both permanently connected to a logical 1. These JK flip-flops are positive edge-triggered (i.e., they change state on the rising edge of the clock). Note that these flip-flops have a CLR ( clear) input that sets Q to 1 when CLR = 1. What does this circuit do?

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Computer Organization And Architecture Themes And Variations

ISBN: 9781111987046

1st Edition

Authors: Alan Clements

Question Posted: