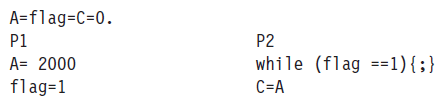

Question: The memory consistency model provides a specification of how the memory system will appear to the programmer. Consider the following code segment, where the initial

a. At the end of the code segment, what is the value you would expect for C?

b. A system with a general-purpose interconnection network, a directory- based cache coherence protocol, and support for nonblocking loads generates a result where C is 0. Describe a scenario where this result is possible.

c. If you wanted to make the system sequentially consistent, what are the key constraints you would need to impose? Assume that a processor supports a relaxed memory consistency model. A relaxed consistency model requires synchronization to be explicitly identified. Assume that the processor supports a €œbarrier€ instruction, which ensures that all memory operations preceding the barrier instruction complete before any memory operations following the barrier are allowed to begin. Where would you include barrier instructions in the above code segment to ensure that you get the €œintuitive results€ of sequential consistency?

A=flag=C=0. P1 P2 while (flag ==1){;} A= 2000 flag=1 C=A

Step by Step Solution

3.45 Rating (174 Votes )

There are 3 Steps involved in it

a Because flag is written only after A is written we ... View full answer

Get step-by-step solutions from verified subject matter experts