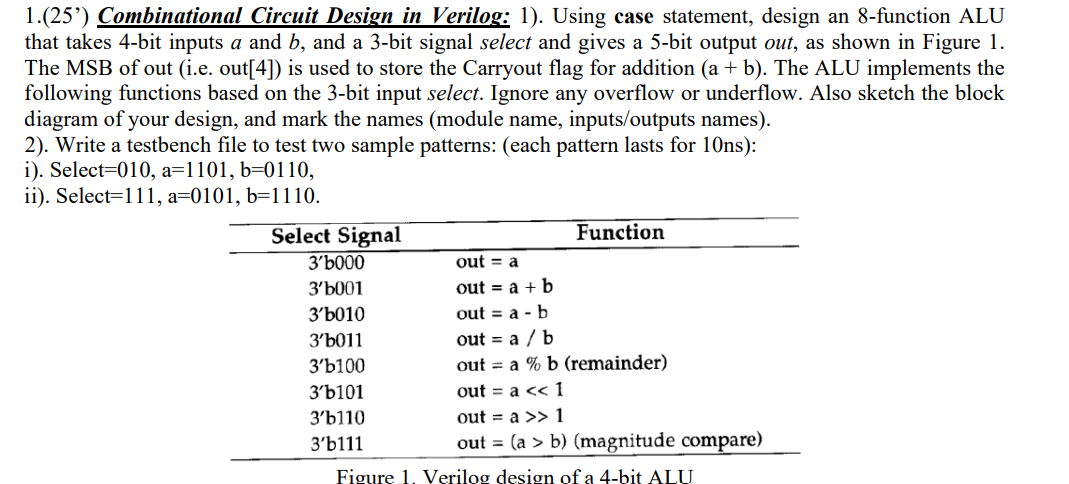

Question: 1 . ( 2 5 ' ) Combinational Circuit Design in Verilog: 1 ) . Using case statement, design an 8 - function ALU that

Combinational Circuit Design in Verilog: Using case statement, design an function ALU

that takes bit inputs a and and a bit signal select and gives a bit output out, as shown in Figure

The MSB of out ie out is used to store the Carryout flag for addition The ALU implements the

following functions based on the bit input select. Ignore any overflow or underflow. Also sketch the block

diagram of your design, and mark the names module name, inputsoutputs names

Write a testbench file to test two sample patterns: each pattern lasts for :

i Select

ii Select

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock