Question: 1) a) Assume a multi-level cache with L1 and L2. Cache line is 16 bytes, both caches are direct-mapped. L1's capacity is 64 bytes, and

1)

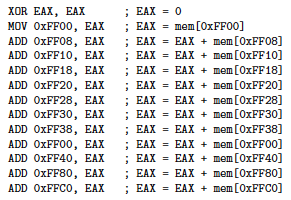

a) Assume a multi-level cache with L1 and L2. Cache line is 16 bytes, both caches are direct-mapped. L1's

capacity is 64 bytes, and L2's capacity is 256 bytes. L1's lookup cost is 2 CPU cycles, whereas L2's

lookup takes 8 cycles. Accessing the memory takes 25 cycles. Assume that each instruction takes 2

cycles to execute. Instructions that accesses the memory have the extracost of loading or storing data

to memory. For the sequence of instructions below, compute the total number of cycles the code takes

to nish. To hide the latency of accessing data, on a cache miss, a stride prefetcher kicks in and requests

data of the address that follows the missed one. For example, if L1 cache misses on address A, and stride

is 1 byte. L1 cache requests data for A and A+1.

b) Assume a multi-level cache (L1 and L2). Memory access pattern shows a stream of addresses where a

stride prefetch is eective. However, the request made by the prefetcher for address A didn't arrive on

time, and a cache miss (on A) happened while there is a outstanding prefetched request on A. What

happens in this case? Is the prefetcher still improving performance (hiding memory access latency)?

c) Assume a multi-level cache (L1 and L2). Memory access pattern shows a stream of addresses where a

stride prefetch is eective. The request made by the prefetcher for address A arrives evicting another

entry, address B, out of the cache. Our program, however, needs the data of B before A. What happens

in this case? Is the prefetcher still improving performance (hiding memory access latency)?

:EAX = 0 ; EAX men(0xFF00] XOR EAX, EAX MOV 0xFF00, EAX; ADD 0xFF08, EAX; ADD 0xFF10, EAX; ADD 0xFF18, EAX ADD 0xFF20, EAX; ADD 0xFF28, EAX; ADD 0xFF30, EAX; ADD 0xFF38, EAX; ADD 0xFF00, EAX; ADD 0xFF40, EAX ADD 0xFF80, EAX; ADD OxFFCO, EAX ; EAX=EAX+men(0xFFC0] EAX = EAX + men(0xFF08] ; EAX = EAX + men(0xFF10] EAX = EAX + men(0xFF18] EAX = EAX + men(0xFF20] EAX = EAX + men(0xFF28] EAX = EAX + men(0xFF30] EAX = EAX + men(0xFF38] EAX = EAX + men(0xFF00] EAX = EAX + men(0xFF40] EAX = EAX + men(0xFF80] :EAX = 0 ; EAX men(0xFF00] XOR EAX, EAX MOV 0xFF00, EAX; ADD 0xFF08, EAX; ADD 0xFF10, EAX; ADD 0xFF18, EAX ADD 0xFF20, EAX; ADD 0xFF28, EAX; ADD 0xFF30, EAX; ADD 0xFF38, EAX; ADD 0xFF00, EAX; ADD 0xFF40, EAX ADD 0xFF80, EAX; ADD OxFFCO, EAX ; EAX=EAX+men(0xFFC0] EAX = EAX + men(0xFF08] ; EAX = EAX + men(0xFF10] EAX = EAX + men(0xFF18] EAX = EAX + men(0xFF20] EAX = EAX + men(0xFF28] EAX = EAX + men(0xFF30] EAX = EAX + men(0xFF38] EAX = EAX + men(0xFF00] EAX = EAX + men(0xFF40] EAX = EAX + men(0xFF80]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts