Question: 1. A pipelined processor has 10 stages and Ins cycle time. A single-cycle processor has 8ns cycle time. a) [5pts] What is the speedup

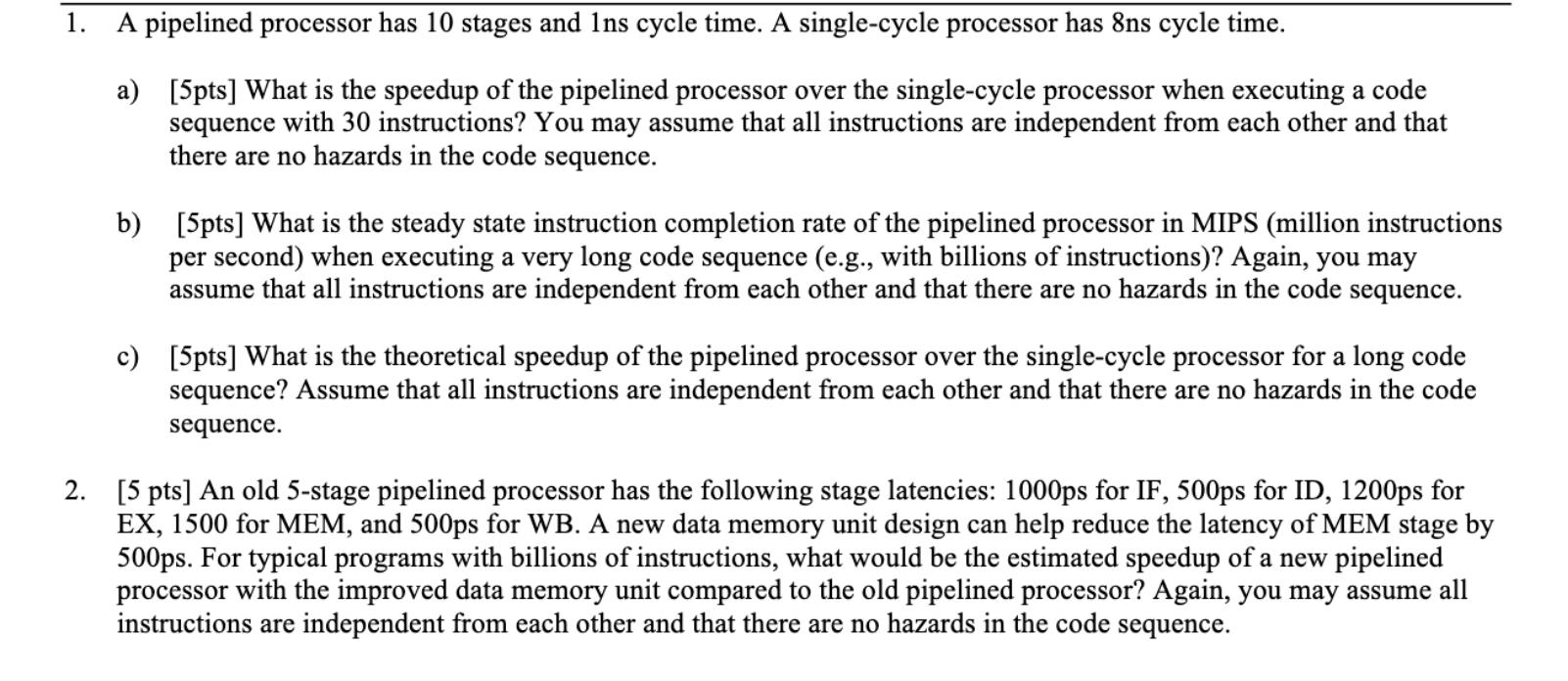

1. A pipelined processor has 10 stages and Ins cycle time. A single-cycle processor has 8ns cycle time. a) [5pts] What is the speedup of the pipelined processor over the single-cycle processor when executing a code sequence with 30 instructions? You may assume that all instructions are independent from each other and that there are no hazards in the code sequence. b) [5pts] What is the steady state instruction completion rate of the pipelined processor in MIPS (million instructions per second) when executing a very long code sequence (e.g., with billions of instructions)? Again, you may assume that all instructions are independent from each other and that there are no hazards in the code sequence. c) [5pts] What is the theoretical speedup of the pipelined processor over the single-cycle processor for a long code sequence? Assume that all instructions are independent from each other and that there are no hazards in the code sequence. 2. [5 pts] An old 5-stage pipelined processor has the following stage latencies: 1000ps for IF, 500ps for ID, 1200ps for EX, 1500 for MEM, and 500ps for WB. A new data memory unit design can help reduce the latency of MEM stage by 500ps. For typical programs with billions of instructions, what would be the estimated speedup of a new pipelined processor with the improved data memory unit compared to the old pipelined processor? Again, you may assume all instructions are independent from each other and that there are no hazards in the code sequence.

Step by Step Solution

There are 3 Steps involved in it

a To calculate the speedup of the pipelined processor over the singlecycle processor we need to compare the execution times of the code sequence with ... View full answer

Get step-by-step solutions from verified subject matter experts