Question: 1. COMPULSORY a) Given the following multiple-output Boolean function, perform both single-output minimization and multiple-output minimization. Compare and discuss the results. $$ begin{array}{1} f=a cdot

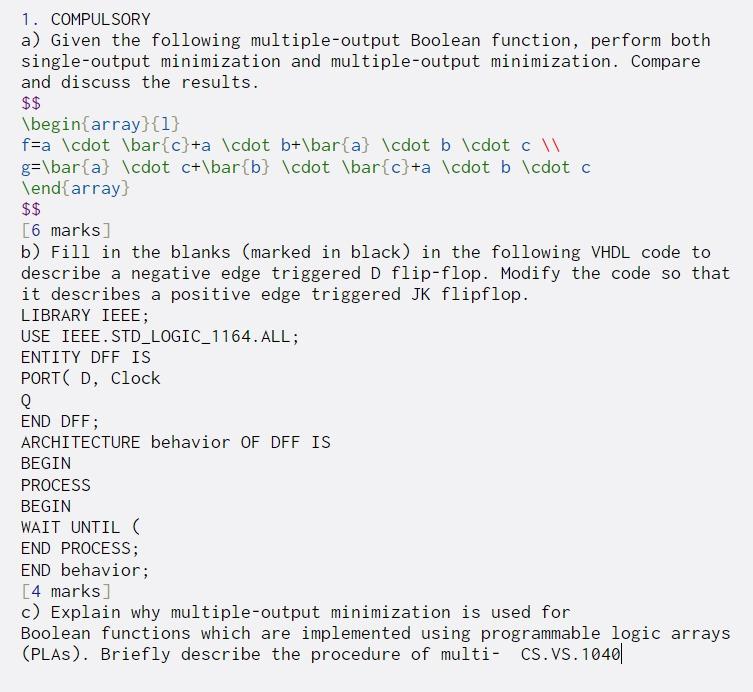

1. COMPULSORY a) Given the following multiple-output Boolean function, perform both single-output minimization and multiple-output minimization. Compare and discuss the results. $$ \begin{array}{1} f=a \cdot \bar{c}+a \cdot b+\bar{a} \cdot b \cdot cl g=\bar{a} \cdot c+\bar{b} \cdot \bar{c}+a \cdot b \cdot c \end{array} $$ [6 marks] b) Fill in the blanks (marked in black) in the following VHDL code to describe a negative edge triggered D flip-flop. Modify the code so that it describes a positive edge triggered JK flipflop. LIBRARY IEEE; USE IEEE. STD_LOGIC_1164.ALL; ENTITY DFF IS PORT D, Clock Q END DFF; ARCHITECTURE behavior OF DFF IS BEGIN PROCESS BEGIN WAIT UNTIL ( END PROCESS; END behavior; [4 marks] c) Explain why multiple-output minimization is used for Boolean functions which are implemented using programmable logic arrays (PLAS). Briefly describe the procedure of multi- CS.VS. 1040|

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts