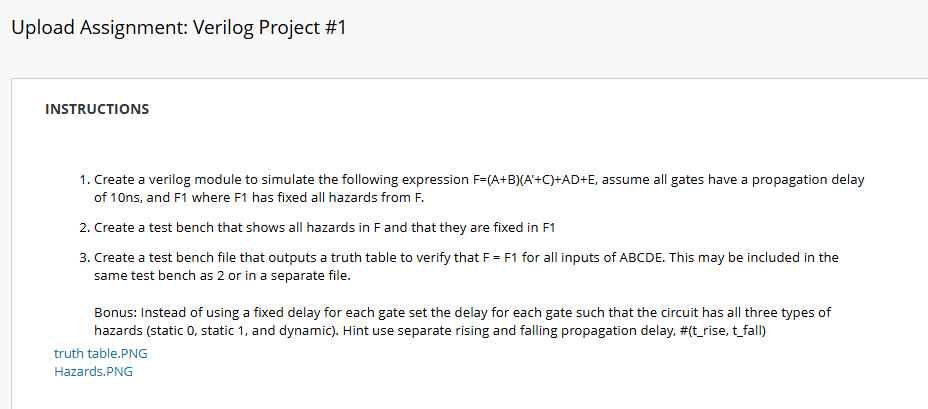

Question: 1 ) Create a verilog module to simulate the following expression F = ( A + B ) ( A ' + C ) +

Create a verilog module to simulate the following expression FABACADE assume all gates have a propagation delay of ns and F where F has fixed all hazards from F

Create a test bench that shows all hazards in F and that they are fixed in F

Create a test bench file that outputs a truth table to verify that F F for all inputs of ABCDE. This may be included in the same test bench as or in a separate file.

Bonus: Instead of using a fixed delay for each gate set the delay for each gate such that the circuit has all three types of hazards static static and dynamic Hint use separate rising and falling propagation delay, #trise, tfall Upload Assignment: Verilog Project #

INSTRUCTIONS

Create a verilog module to simulate the following expression mathrmFmathrmAmathrmBleftmathrmAprimemathrmCrightmathrmADmathrmE assume all gates have a propagation delay of ns and F where F has fixed all hazards from F

Create a test bench that shows all hazards in F and that they are fixed in F

Create a test bench file that outputs a truth table to verify that FF for all inputs of A B C D E This may be included in the same test bench as or in a separate file.

Bonus: Instead of using a fixed delay for each gate set the delay for each gate such that the circuit has all three types of hazards static static and dynamic Hint use separate rising and falling propagation delay, #trise, tfall

truth table.PNG

Hazards.PNG

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock