Question: 1) Design a finite state machine to model a specified counting sequence counter. The initial or reset state of the counter is 000. The predefined

1) Design a finite state machine to model a specified counting sequence counter. The initial or reset state of the counter is 000. The predefined counting sequence is 000 110 111 011 010 101 000 .

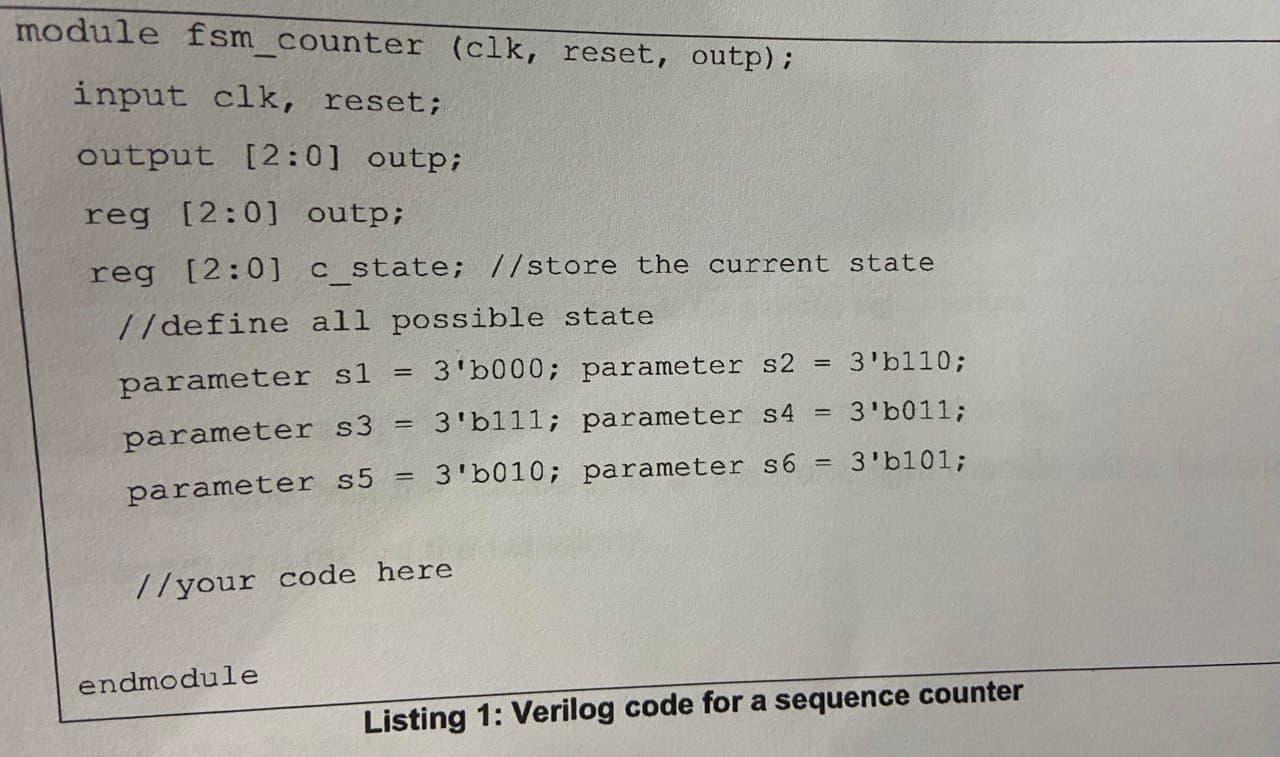

2) Create a new project file (fsm_counter.v) and implement the counter designed in Step 1 using Verilog entry with Quartus Prime. a. The counter should have at least two input (clock and reset). b. Use a single initial block to initialize the initial state for the finite state machine. c. Use a single always block to compute the next logic state based on the clock or reset signal. d. Partial listing of the code is shown in Listing 1. 3

3) Compile and verify the design. Fix any errors that exist.

4) Simulate and test the functionality of the sequence counter using ModelSimIntel FPGA. Observe and record the waveform.

module fsm_counter (clk, reset, outp); input clk, reset; output [2:0] outp; reg [2:0] outp; reg (2:0) c_state; //store the current state //define all possible state parameter sl = 3'5000; parameter s2 = 3'b110; parameter s3 3'b111; parameter s4 3'b011; parameter 55 = 3'b010; parameter s6 3'b101; [/your code here endmodule Listing 1: Verilog code for a sequence counter

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts