Question: 1. In class we derived and provided rationale for a simple delay model in which the delay of a gate is proportional to the number

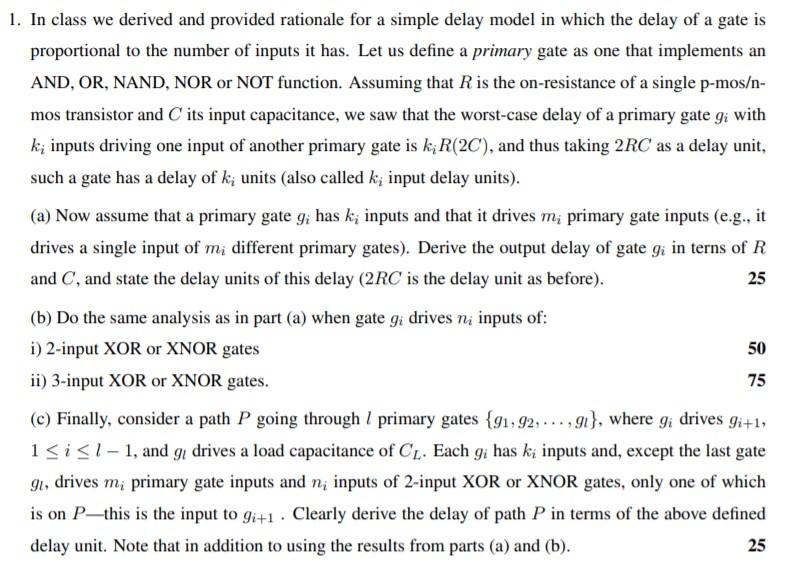

1. In class we derived and provided rationale for a simple delay model in which the delay of a gate is proportional to the number of inputs it has. Let us define a primary gate as one that implements an AND, OR, NAND, NOR or NOT function. Assuming that R is the on-resistance of a single p-mos- mos transistor and C its input capacitance, we saw that the worst-case delay of a primary gate gi with k; inputs driving one input of another primary gate is kiR(2C), and thus taking 2RC as a delay unit, such a gate has a delay of k; units (also called k; input delay units). (a) Now assume that a primary gate gi has k; inputs and that it drives mi primary gate inputs (e.g., it drives a single input of mi different primary gates). Derive the output delay of gate gi in terns of R and C, and state the delay units of this delay (2RC is the delay unit as before). 25 (b) Do the same analysis as in part (a) when gate gi drives ni inputs of: i) 2-input XOR or XNOR gates 50 ii) 3-input XOR or XNOR gates. 75 (c) Finally, consider a path P going through / primary gates {91,92,...,91}, where gi drives 9i+1, 1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts