Question: 1. Modify the codegiven in the lecture for the up-counter so that it creates an up-down counter with 4 bits. The decision to countup or

![reset, counter_out); 2 3 input clk, reset; 4 output [1:0] counter_out; 5](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2022/11/6384e462eead1_6026384e462a4cf7.jpg)

- 1. Modify the codegiven in the lecture for the up-counter so that it creates anup-down counter with 4 bits. The decision to countup or down is made by the value of the input signalw. If w is 0, the counter will count up. Ifw is 1, the counter will count down. This counter should countevery positive edge of the clock signal. The counter should resetto the initial state (0000 or 1111) every positive edge of theresetsignal.

1- Insert the Verilog code of the counter module and comment itin detail

2- Insert a screenshot of the simulation for the up-downcounter.

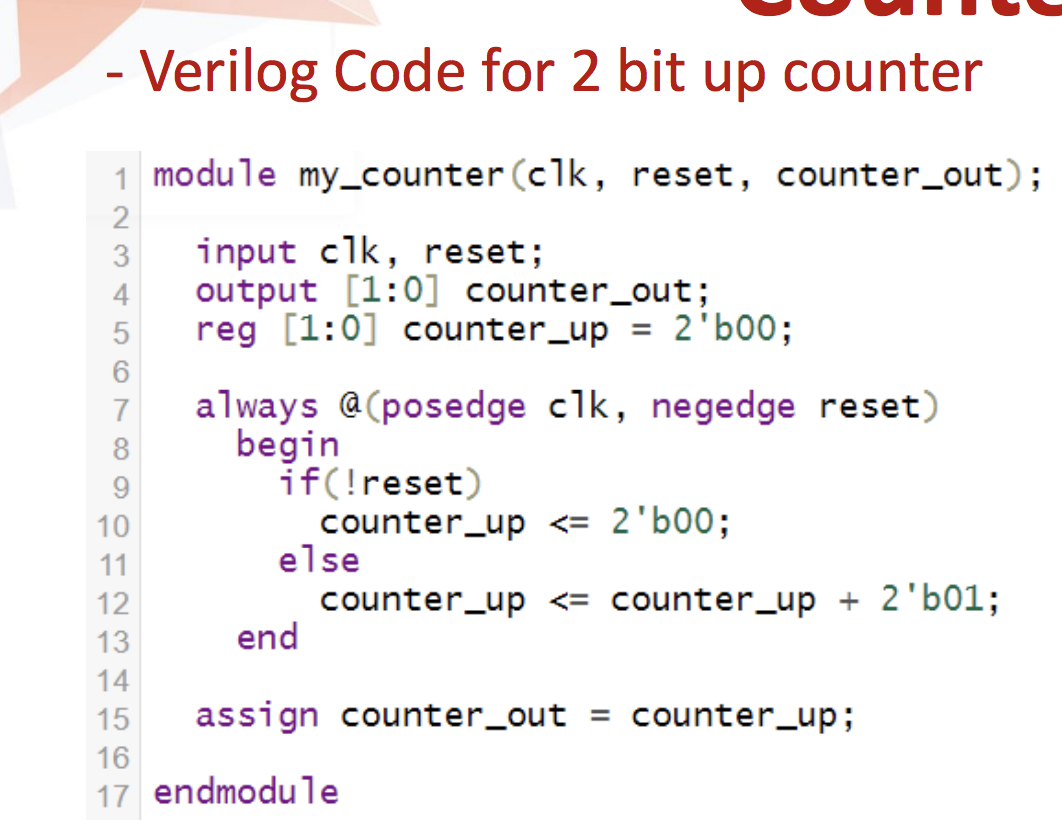

- Verilog Code for 2 bit up counter 1 module my_counter (clk, reset, counter_out); 2 3 input clk, reset; 4 output [1:0] counter_out; 5 6 7 9 10 11 12 13 14 15 reg [1:0] counter_up = 2 b00; always @(posedge clk, negedge reset) begin if(!reset) counter_up 1 module mycounter_testbench(); 2 reg clk, reset; 3 wire [1:0] counter_out; my_counter test (clk, reset, counter_out); 7 initial begin 8 clk 0: 9 forever #2 clk=~clk; 10 end 11 12 initial begin 13 reset=0; 14 #1; 15 reset=1; 16 end 17 18 19 20 21 22 23 initial begin #1; $display( worked by: Instructor ); $display( Counter output = %b ,counter_out); #4; $display( Counter output = %b ,counter_out); #4; $display( Counter output %b ,counter_out); #4; $display( Counter output = %b counter_out); #4; $display( Counter output = %b ,counter_out); #4; $display( Counter output = %b ,counter_out); #4; $display( Counter output = %b ,counter_out); #4; 24 25 26 27 28 29 30 31 endmodule end

Step by Step Solution

There are 3 Steps involved in it

Heres the modified Verilog code for the 4bit updown counter module updowncounter input clk Clock ... View full answer

Get step-by-step solutions from verified subject matter experts