Question: 1. Suppose you could build a CPU where the clock cycle time was different for each instruction. What would the speedup of this new CPU

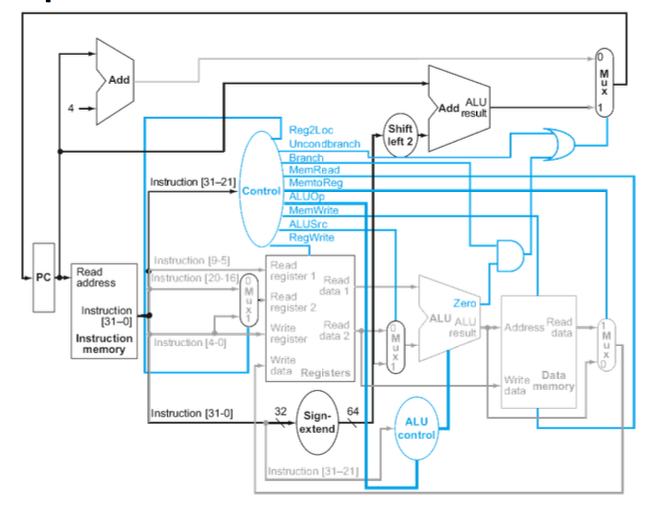

1. Suppose you could build a CPU where the clock cycle time was different for each instruction. What would the speedup of this new CPU be over the CPU presented in Figure 4.23 in the book (also in Chapter 4, slide 25) given the instruction mix below?

Figure 4.23

2. Examine the difficulty of adding a proposed ss Rd, Rn, #immediate (Store sum) instruction to the LEGv8 instruction set, which works as follows: Mem[Reg[Rd]]=Reg[Rn]+immediate;

a. Which new functional blocks (if any) do we need for this instruction?

b. Which existing functional blocks (if any) require modification?

c. What new datapaths do we need (if any) to support this instruction?

d. What new control unit signals (if any) do we need for this instruction?

e. Modify the complete control and datapath Figure to demonstrate the implementation of this new instruction. Use Figure 4.23, also shown in Chapter 4 slides, Slide 25.

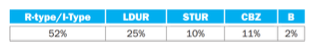

CBZ LDUR 25% STUR R-type/I-Type 52% 10% 11% 12% CBZ LDUR 25% STUR R-type/I-Type 52% 10% 11% 12%

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts