Question: 1) Write VHDL model of a combinational logic circuit that has an 8-bit bus input, a 4-bit bus output and a single bit output. The

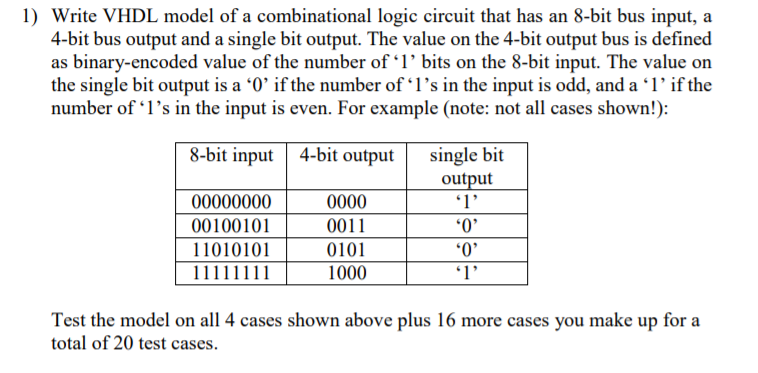

1) Write VHDL model of a combinational logic circuit that has an 8-bit bus input, a 4-bit bus output and a single bit output. The value on the 4-bit output bus is defined as binary-encoded value of the number of 'l' bits on the 8-bit input. The value on the single bit output is a Oif the number of 'l's in the input is odd, and a lif the number of 'l's in the input is even. For example (note: not all cases shown!): 8-bit input 4-bit output 00000000 00100101 11010101 11111111 0000 0011 0101 1000 single bit output 1 O' '0' l' Test the model on all 4 cases shown above plus 16 more cases you make up for a total of 20 test cases. 1) Write VHDL model of a combinational logic circuit that has an 8-bit bus input, a 4-bit bus output and a single bit output. The value on the 4-bit output bus is defined as binary-encoded value of the number of 'l' bits on the 8-bit input. The value on the single bit output is a Oif the number of 'l's in the input is odd, and a lif the number of 'l's in the input is even. For example (note: not all cases shown!): 8-bit input 4-bit output 00000000 00100101 11010101 11111111 0000 0011 0101 1000 single bit output 1 O' '0' l' Test the model on all 4 cases shown above plus 16 more cases you make up for a total of 20 test cases

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts