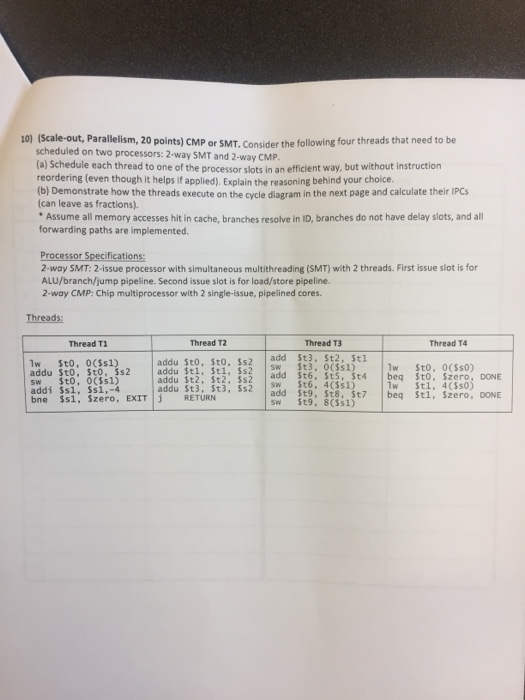

Question: 10) (Scale-out, Parallelism, 20 points) CMP or SMT. Consider the following four threads that need to be scheduled on two processors: 2-way SMT and 2-way

10) (Scale-out, Parallelism, 20 points) CMP or SMT. Consider the following four threads that need to be scheduled on two processors: 2-way SMT and 2-way CMP (a) Schedule each thread to one of th reordering (even though it helps if applied), Explain the reasoning behind your choice. (b) Demonstrate how the threads execute on the cycle diagram in the next page and calculate their IPCs (can leave as fractions). Assume all memory accesses hit in cache, branches resolve in ID, branches do not have delay slots, and all e processor slots in an efficient way forwarding paths are implemented. essor 2-way SMT: 2-issue processor with simultaneous multithreading (SMT) with 2 threads. First issue slot is for ALU/branch/jump pipeline. Second issue slot is for load/store pipeline. 2-way CMP: Chip multiprocessor with 2 single-issue, pipelined cores. Threads: Thread T1 Thread T2 Thread T3 Thread T4 add St3, St2, $tl $to , sro, $s2 | awa St, addu O($51) addu Sto, St0, Ss2 addi $sl, Ss1,-4 bne Ss1, Szero, EXIT RETURN Sto, Szero, DONE beq St1, Szero, DONE sw $t9, 8(3s1) 10) (Scale-out, Parallelism, 20 points) CMP or SMT. Consider the following four threads that need to be scheduled on two processors: 2-way SMT and 2-way CMP (a) Schedule each thread to one of th reordering (even though it helps if applied), Explain the reasoning behind your choice. (b) Demonstrate how the threads execute on the cycle diagram in the next page and calculate their IPCs (can leave as fractions). Assume all memory accesses hit in cache, branches resolve in ID, branches do not have delay slots, and all e processor slots in an efficient way forwarding paths are implemented. essor 2-way SMT: 2-issue processor with simultaneous multithreading (SMT) with 2 threads. First issue slot is for ALU/branch/jump pipeline. Second issue slot is for load/store pipeline. 2-way CMP: Chip multiprocessor with 2 single-issue, pipelined cores. Threads: Thread T1 Thread T2 Thread T3 Thread T4 add St3, St2, $tl $to , sro, $s2 | awa St, addu O($51) addu Sto, St0, Ss2 addi $sl, Ss1,-4 bne Ss1, Szero, EXIT RETURN Sto, Szero, DONE beq St1, Szero, DONE sw $t9, 8(3s1)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts