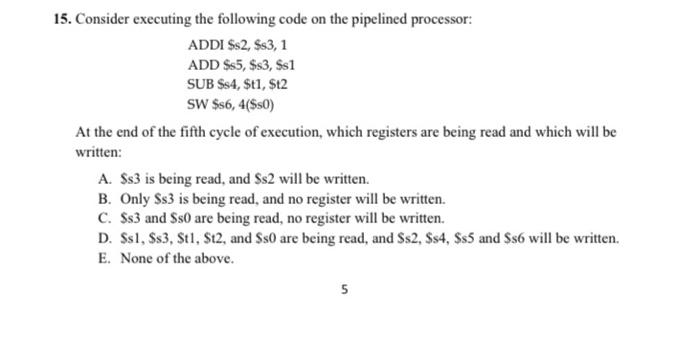

Question: 15. Consider executing the following code on the pipelined processor: ADDI $s2, S3, 1 ADD $85, $s3, Ss1 SUB Ss4, $t1,$t2 SW $56, 4($0) At

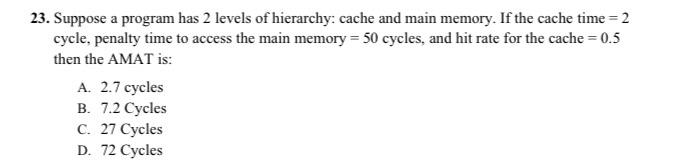

15. Consider executing the following code on the pipelined processor: ADDI $s2, S3, 1 ADD $85, $s3, Ss1 SUB Ss4, $t1,$t2 SW $56, 4($0) At the end of the fifth cycle of execution, which registers are being read and which will be written: A. $s3 is being read, and Ss2 will be written. B. Only $s3 is being read, and no register will be written. C. $s3 and $50 are being read, no register will be written. D. Ssl, $s3, $t1, $12, and Ss are being read, and $s2, S4, Ss5 and Ss6 will be written. E. None of the above. 5 23. Suppose a program has 2 levels of hierarchy: cache and main memory. If the cache time = 2 cycle, penalty time to access the main memory = 50 cycles, and hit rate for the cache = 0.5 then the AMAT is: A. 2.7 cycles B. 7.2 Cycles C. 27 Cycles D. 72 Cycles

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts