Question: (15 points) Generalized Counter Design: Interpreting counters as finite state machines. You are asked to design a synchronous 3-bit counter that advances through the sequence:

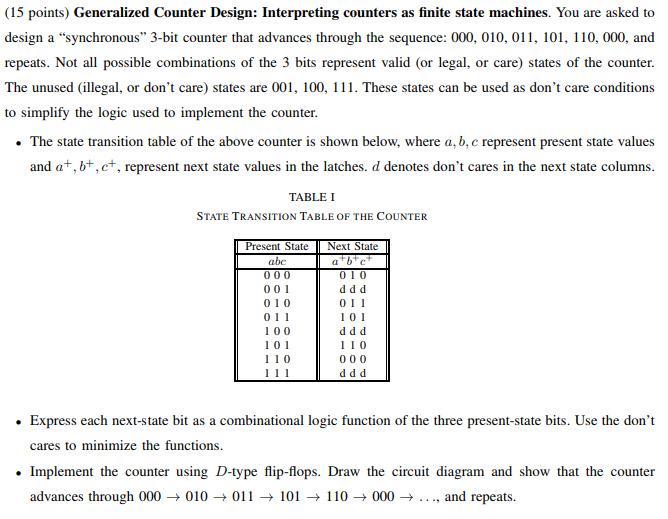

(15 points) Generalized Counter Design: Interpreting counters as finite state machines. You are asked to design a "synchronous" 3-bit counter that advances through the sequence: 000, 010, 011, 101, 110, 000, and repeats. Not all possible combinations of the 3 bits represent valid (or legal, or care) states of the counter. The unused (illegal, or don't care) states are 001, 100, 111. These states can be used as don't care conditions to simplify the logic used to implement the counter. The state transition table of the above counter is shown below, where a, b, c represent present state values and a+,b+,c+, represent next state values in the latches. d denotes don't cares in the next state columns TABLE I STATE TRANSITION TABLE OF THE COUNTER ate abc 001 0 10 0 11 1 0 0 0 11 l 1 0 . Express each next-state bit as a combinational logic function of the three present-sta te bits. Use the don't cares to minimize the functions Implement the counter using D-type flip-flops. Draw the circuit diagram and show that the counter advances through 000010011 101110000 -> ..., and repeats

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts