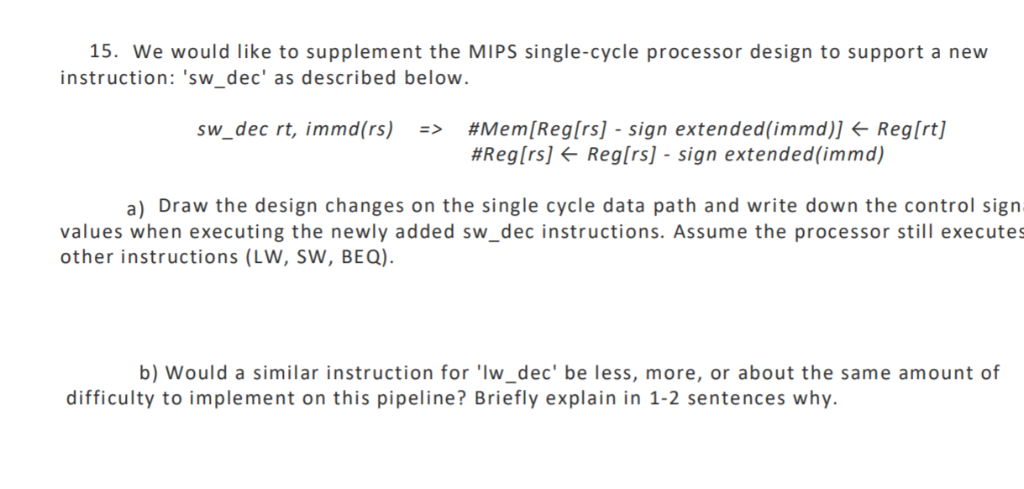

Question: 15. We would like to supplement the MIPS single-cycle processor design to support a new instruction: 'sw_dec' as described below. sw-dec rt, immd(rs) #Mem[Reg[rs] -sign

15. We would like to supplement the MIPS single-cycle processor design to support a new instruction: 'sw_dec' as described below. sw-dec rt, immd(rs) #Mem[Reg[rs] -sign extended(immd)] Reg[rt] #Reg[rs] a) Draw the design changes on the single cycle data path and write down the control sign values when executing the newly added sw_dec instructions. Assume the processor still executes other instructions (LW, SW, BEQ) b) Would a similar instruction for 'Iw_dec' be less, more, or about the same amount of difficulty to implement on this pipeline? Briefly explain in 1-2 sentences why 15. We would like to supplement the MIPS single-cycle processor design to support a new instruction: 'sw_dec' as described below. sw-dec rt, immd(rs) #Mem[Reg[rs] -sign extended(immd)] Reg[rt] #Reg[rs] a) Draw the design changes on the single cycle data path and write down the control sign values when executing the newly added sw_dec instructions. Assume the processor still executes other instructions (LW, SW, BEQ) b) Would a similar instruction for 'Iw_dec' be less, more, or about the same amount of difficulty to implement on this pipeline? Briefly explain in 1-2 sentences why

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts