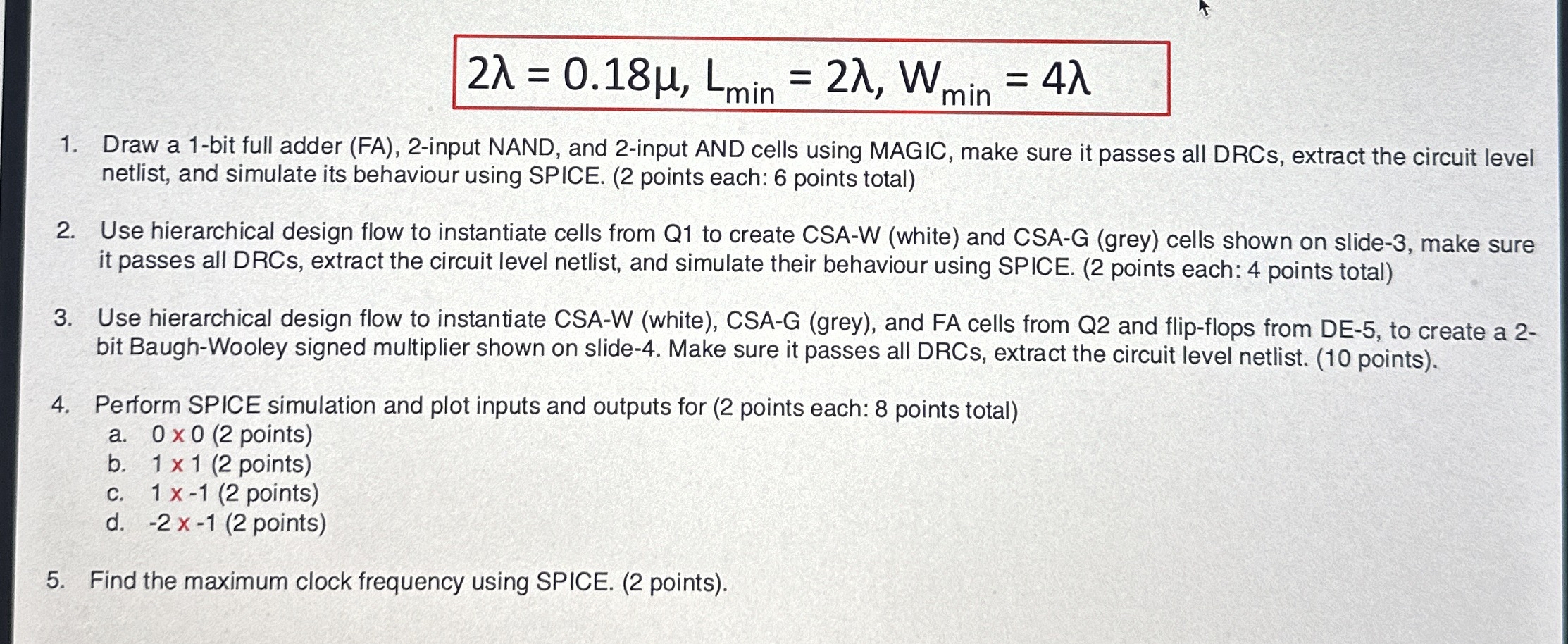

Question: 2 = 0 . 1 8 , L m i n = 2 , W m i n = 4 Draw a 1 - bit

Draw a bit full adder FAinput NAND, and input AND cells using MAGIC, make sure it passes all DRCs extract the circuit level netlist, and simulate its behaviour using SPICE. points each: points total

Use hierarchical design flow to instantiate cells from Q to create CSAW white and CSAG grey cells shown on slide make sure it passes all DRCs extract the circuit level netlist, and simulate their behaviour using SPICE. points each: points total

Use hierarchical design flow to instantiate CSAW white CSAG grey and FA cells from Q and flipflops from DE to create a bit BaughWooley signed multiplier shown on slide Make sure it passes all DRCs extract the circuit level netlist. points

Perform SPICE simulation and plot inputs and outputs for points each: points total

a points

b points

c points

d points

Find the maximum clock frequency using SPICE. points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock