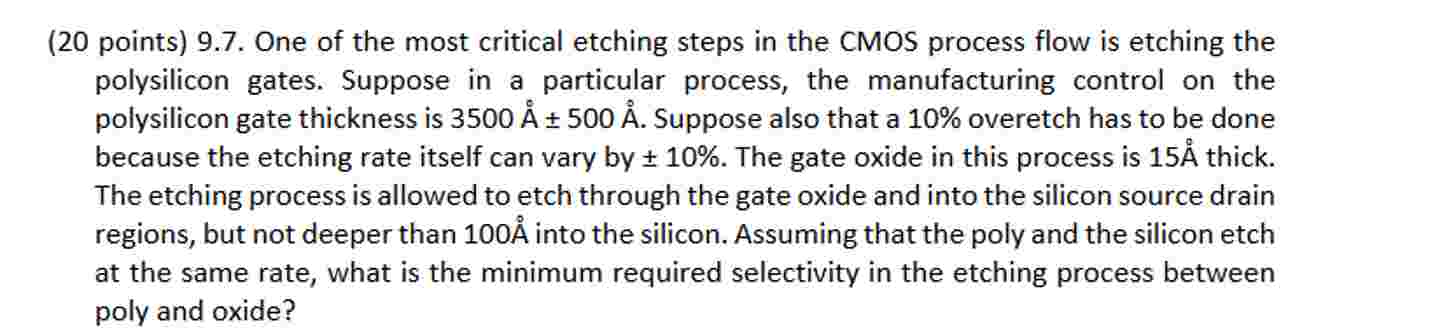

Question: ( 2 0 points ) 9 . 7 . One of the most critical etching steps in the CMOS process flow is etching the polysilicon

points One of the most critical etching steps in the CMOS process flow is etching the polysilicon gates. Suppose in a particular process, the manufacturing control on the polysilicon gate thickness is AA pm AA Suppose also that a overetch has to be done because the etching rate itself can vary by pm The gate oxide in this process is AA thick. The etching process is allowed to etch through the gate oxide and into the silicon source drain regions, but not deeper than AA into the silicon. Assuming that the poly and the silicon etch at the same rate, what is the minimum required selectivity in the etching process between poly and oxide?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock