Question: 2. (40 points, 20 pts each) Consider the RISC computer (byte-addressable with 32-bit words) with a 5- stage pipelined data path. Registers R4, R5, and

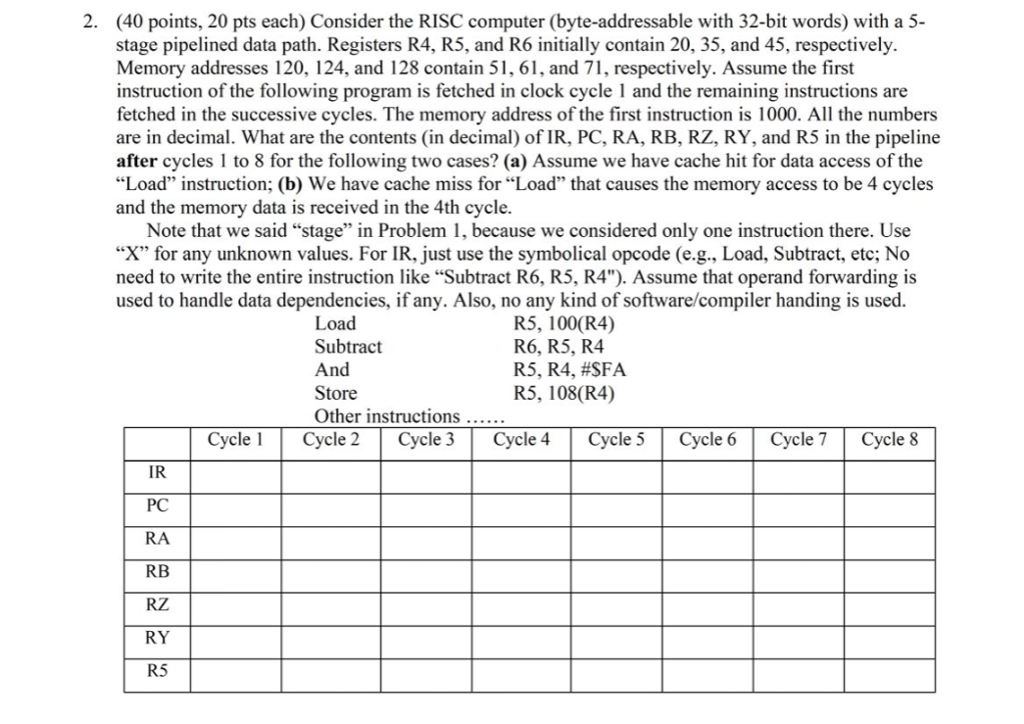

2. (40 points, 20 pts each) Consider the RISC computer (byte-addressable with 32-bit words) with a 5- stage pipelined data path. Registers R4, R5, and R6 initially contain 20, 35, and 45, respectively Memory addresses 120, 124, and 128 contain 51, 61, and 71, respectively. Assume the first instruction of the following program is fetched in clock cycle 1 and the remaining instructions are fetched in the successive cycles. The memory address of the first instruction is 1000. All the numbers are in decimal. What are the contents (in decimal) of IR, PC, RA, RB, RZ, RY, and R5 in the pipeline after cycles 1 to 8 for the following two cases? (a) Assume we have cache hit for data access of the "Load" instruction; (b) We have cache miss for "Load" that causes the memory access to be 4 cycles and the memory data is received in the 4th cycle. Note that we said "stage" in Problem 1, because we considered only one instruction there. Use "X" for any unknown values. For IR, Just use the symbolical opcode (eg, Load, Subtract, etc; No need to write the entire instruction like "Subtract R6, R5, R4"). Assume that operand forwarding is used to handle data dependencies, if any. Also, no any kind of software/compiler handing is used. oa Subtract And Store Other instructions R5, 100(R4) R6. R5, R4 R5, R4, #$FA R5, 108(R4) CycleCycle 2Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7Cycle 8 IR PC RA RB RZ RY R5 2. (40 points, 20 pts each) Consider the RISC computer (byte-addressable with 32-bit words) with a 5- stage pipelined data path. Registers R4, R5, and R6 initially contain 20, 35, and 45, respectively Memory addresses 120, 124, and 128 contain 51, 61, and 71, respectively. Assume the first instruction of the following program is fetched in clock cycle 1 and the remaining instructions are fetched in the successive cycles. The memory address of the first instruction is 1000. All the numbers are in decimal. What are the contents (in decimal) of IR, PC, RA, RB, RZ, RY, and R5 in the pipeline after cycles 1 to 8 for the following two cases? (a) Assume we have cache hit for data access of the "Load" instruction; (b) We have cache miss for "Load" that causes the memory access to be 4 cycles and the memory data is received in the 4th cycle. Note that we said "stage" in Problem 1, because we considered only one instruction there. Use "X" for any unknown values. For IR, Just use the symbolical opcode (eg, Load, Subtract, etc; No need to write the entire instruction like "Subtract R6, R5, R4"). Assume that operand forwarding is used to handle data dependencies, if any. Also, no any kind of software/compiler handing is used. oa Subtract And Store Other instructions R5, 100(R4) R6. R5, R4 R5, R4, #$FA R5, 108(R4) CycleCycle 2Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7Cycle 8 IR PC RA RB RZ RY R5

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts