Question: 2 . A digital system - on - chip in a 1 - V 6 5 nm process ( with 5 0 nm drawn channel

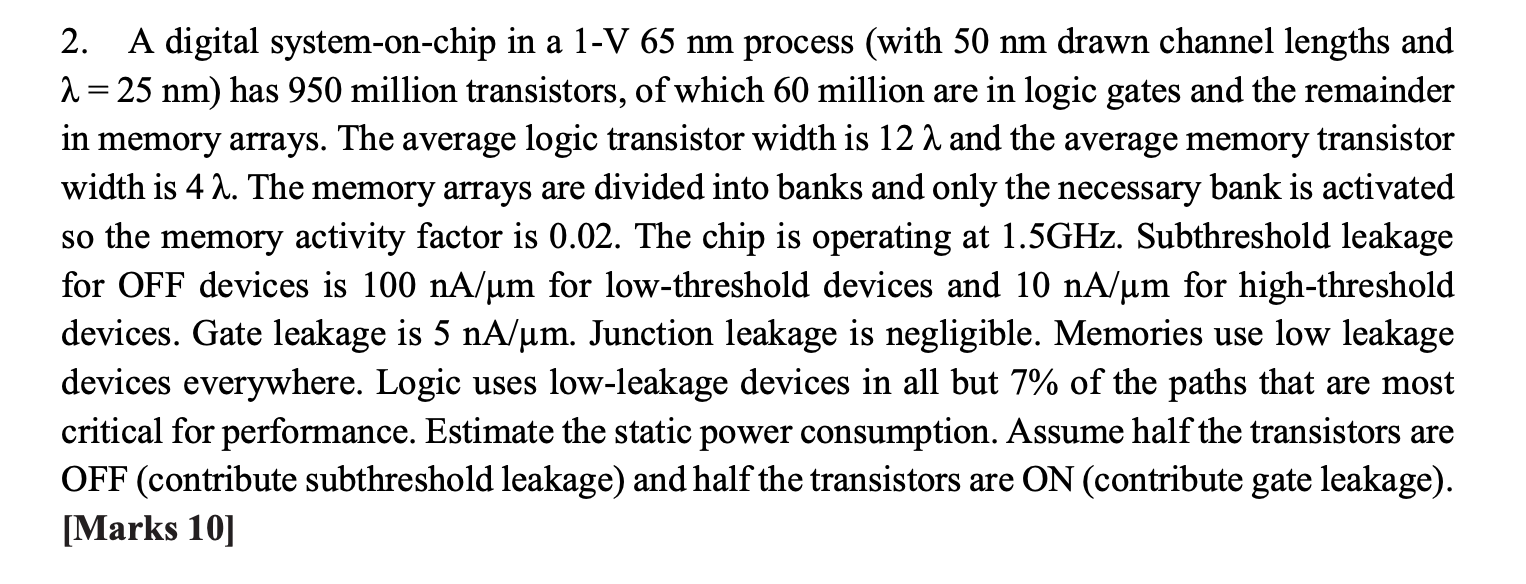

A digital systemonchip in a V nm process with nm drawn channel lengths and lambdamathrm~nm has million transistors, of which million are in logic gates and the remainder in memory arrays. The average logic transistor width is lambda and the average memory transistor width is lambda The memory arrays are divided into banks and only the necessary bank is activated so the memory activity factor is The chip is operating at GHz Subthreshold leakage for OFF devices is mathrmnAmu mathrmm for lowthreshold devices and mathrmnAmu mathrmm for highthreshold devices. Gate leakage is mathrmnAmu mathrmm Junction leakage is negligible. Memories use low leakage devices everywhere. Logic uses lowleakage devices in all but of the paths that are most critical for performance. Estimate the static power consumption. Assume half the transistors are OFF contribute subthreshold leakage and half the transistors are ON contribute gate leakageMarks

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock