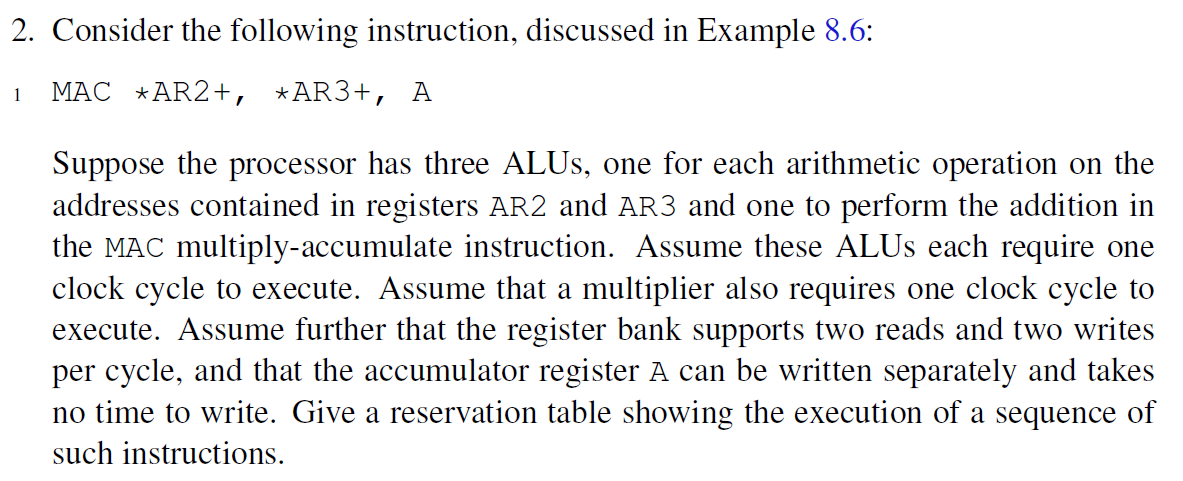

Question: 2. Consider the following instruction, discussed in Example 8.6: 1 MAC *AR2+, AR3+, A Suppose the processor has three ALUs, one for each arithmetic operation

2. Consider the following instruction, discussed in Example 8.6: 1 MAC *AR2+, AR3+, A Suppose the processor has three ALUs, one for each arithmetic operation on the addresses contained in registers AR2 and AR3 and one to perform the addition in the MAC multiply-accumulate instruction. Assume these ALUS each require one clock cycle to execute. Assume that a multiplier also requires one clock cycle to execute. Assume further that the register bank supports two reads and two writes per cycle, and that the accumulator register A can be written separately and takes no time to write. Give a reservation table showing the execution of a sequence of such instructions. 2. Consider the following instruction, discussed in Example 8.6: 1 MAC *AR2+, AR3+, A Suppose the processor has three ALUs, one for each arithmetic operation on the addresses contained in registers AR2 and AR3 and one to perform the addition in the MAC multiply-accumulate instruction. Assume these ALUS each require one clock cycle to execute. Assume that a multiplier also requires one clock cycle to execute. Assume further that the register bank supports two reads and two writes per cycle, and that the accumulator register A can be written separately and takes no time to write. Give a reservation table showing the execution of a sequence of such instructions

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts