Question: 2. From the following assembly language code for a 32-bit MIPS processor, generate the binary machine language for this code fragment. Consult the Internet, for

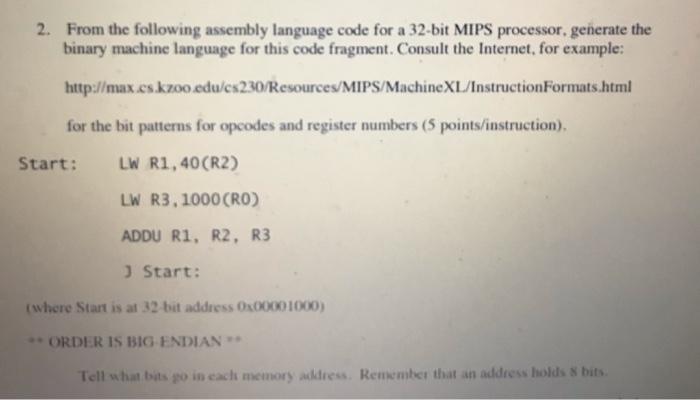

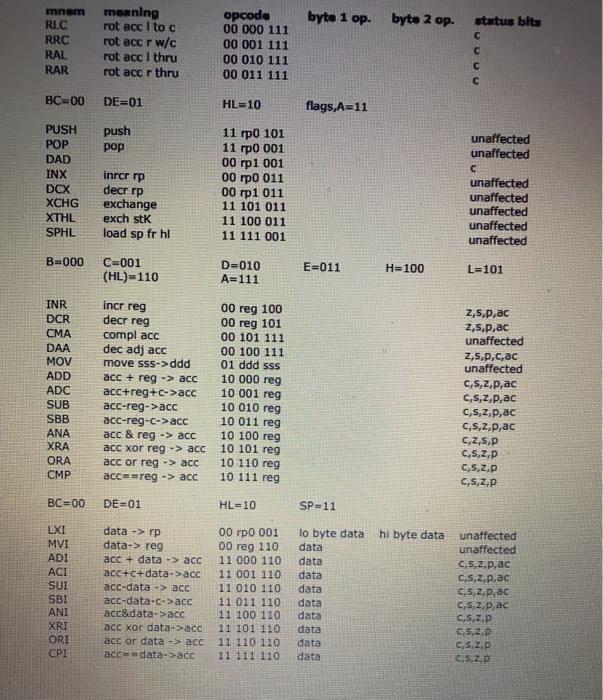

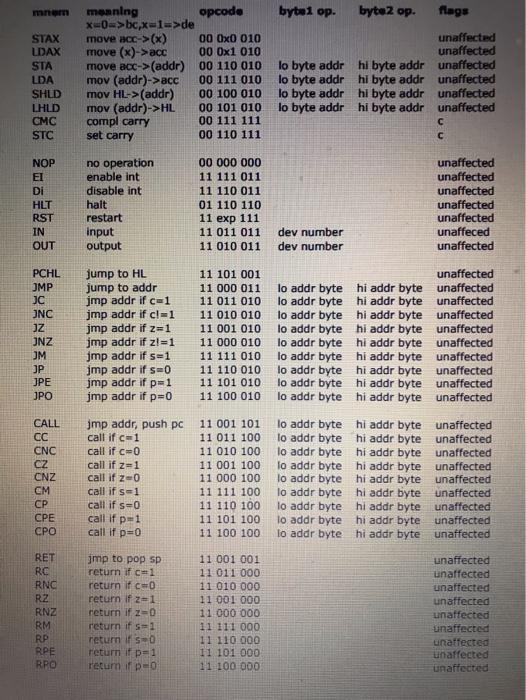

2. From the following assembly language code for a 32-bit MIPS processor, generate the binary machine language for this code fragment. Consult the Internet, for example: http://max.es.kzoo edu/cs230/Resources/MIPS/Machine XL/Instruction Formats.html for the bit patterns for opcodes and register numbers (5 points/instruction), Start: LW R1, 40(R2) LW R3, 1000(RO) ADDU R1, R2, R3 J Start: (where Start is at 32 bit address Ox00001000) ORDER IS BIG ENDIAN Tell what bitspo in each memory address. Remember that an address holds 8 bits byte 1 op. byte 2 op. mnom RLC RRC RAL RAR meaning rot acc I toc rot acc r w/c rot acc I thru rot acc r thru opcode 00 000 111 00 001 111 00 010 111 00 011 111 status bits C BC-00 DE=01 HL=10 flags, A=11 push pop PUSH POP DAD INX DCX XCHG XTHL SPHL inrcr rp decr rp exchange exch stk load sp fr hl 11 rp0 101 11 rp0 001 00 rp1 001 00 rp0 011 00 rp1 011 11 101 011 11 100 011 11 111 001 unaffected unaffected C unaffected unaffected unaffected unaffected unaffected B.000 C=001 (HL)-110 D=010 A=111 E-011 H=100 L=101 incr reg decr reg INR DCR CMA DAA MOV ADD ADC SUB SBB ANA XRA ORA CMP compl acc dec adj acc move sss->ddd acc + reg -> acc acc+reg+C->acc acc-reg->acc acc-reg-C->acc acc & reg -> acc acc xor reg -> acc acc or reg -> acc accareg -> acc 00 reg 100 00 reg 101 00 101 111 00 100 111 01 ddd sss 10 000 reg 10 001 reg 10 010 reg 10 011 reg 10 100 reg 10 101 reg 10 110 reg 10 111 reg Z,S,P,ac 2,5.p,ac unaffected Z,S.P.c,ac unaffected C,S,Z,P,ac C,S,2,P,ac C,S,z,P,ac C,S,2,P,ac C,2,5,P C,S,Z,P C.5,2,P C,S,Z,P BC=00 DE01 HL=10 SP=11 hi byte data LXI MVI ADI ACI SUI SBI ANI XRI ORI CPI data -> TP data-> reg acc + data -> acc acc+C+data->acc acc-data -> acc acc-data-C->acc acc&data-acc aco xor data->acc acc or data -> acc accdata-acc 00 rp0 001 00 reg 110 11 000 110 11 001 110 11 010 110 11 011 110 11 100 110 11 101 110 11 110 110 11 111 110 To byte data data data data data data data data data data unaffected unaffected C.S.Z.P.ac C,S,2,p.ac 0.5,2,p.ac C,S,2,P,ac C,S,P C.5,2,P C,S,Z,P C.5,2, mnom byte1 op. byte2 op. flags STAX LDAX STA LDA SHLD LHLD CMC STC meaning opcode X=0->bc,x=1=>de move acc->(x) 00 Ox0 010 move (x)-> acc 00 Ox1 010 move acc->(addr) 00 110 010 mov (addr)->acc 00 111 010 mov HL-> (addr) 00 100 010 mov (addr)->HL 00 101 010 compl carry 00 111 111 00 110 111 unaffected unaffected lo byte addr hi byte addrunaffected lo byte addr hi byte addr unaffected lo byte addr hi byte addrunaffected lo byte addr hi byte addrunaffected set carry NOP Di HLT RST IN OUT no operation enable int disable int hait restart input output 00 000 000 11 111 011 11 110 011 01 110 110 11 exp 111 11 011 011 11 010 011 unaffected unaffected unaffected unaffected unaffected unaffeced unaffected dev number dev number PCHL JMP JC JNC JZ JNZ JM JP JPE JPO jump to HL jump to addr jmp addr if c=1 jmp addr if c=1 jmp addr if z=1 jmp addr if zl=1 jmp addr if s=1 jmp addr if s=0 jmp addr if p1 jmp addr if p=0 11 101 001 11 000 011 11 011 010 11 010 010 11 001 010 11 000 010 11 111 010 11 110 010 11 101 010 11 100 010 unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected CALL CC CNC CZ CNZ CM CP CPE jmp addr, push pc call if c1 call if c=0 call if Z=1 call if 2-0 call ifs=1 call if s=0 call if p1 call if p=0 11 001 101 11 011 100 11 010 100 11 001 100 11 000 100 11 111 100 11 110 100 11 101 100 11 100 100 lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected lo addr byte hi addr byte unaffected RET RC RNC R2 RNZ RM RP RPE RPO gmp to pop sp return if #1 return if co return f z=1 return if z=0 return ifs=1 return if so return fp=1 return if peo 11 001 001 11 011 000 11 010 000 11 001 000 11 000 000 11 111 000 11 110 000 11 101 000 11 100 000 unaffected unaffected unaffected unaffected unaffected unaffected unaffected unaffected unaffected

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts