Question: 2 loads, or 2 stores, or 1 load and 1 store vector operation at the same time, one wipelined vector multiplier and one pipelined vector

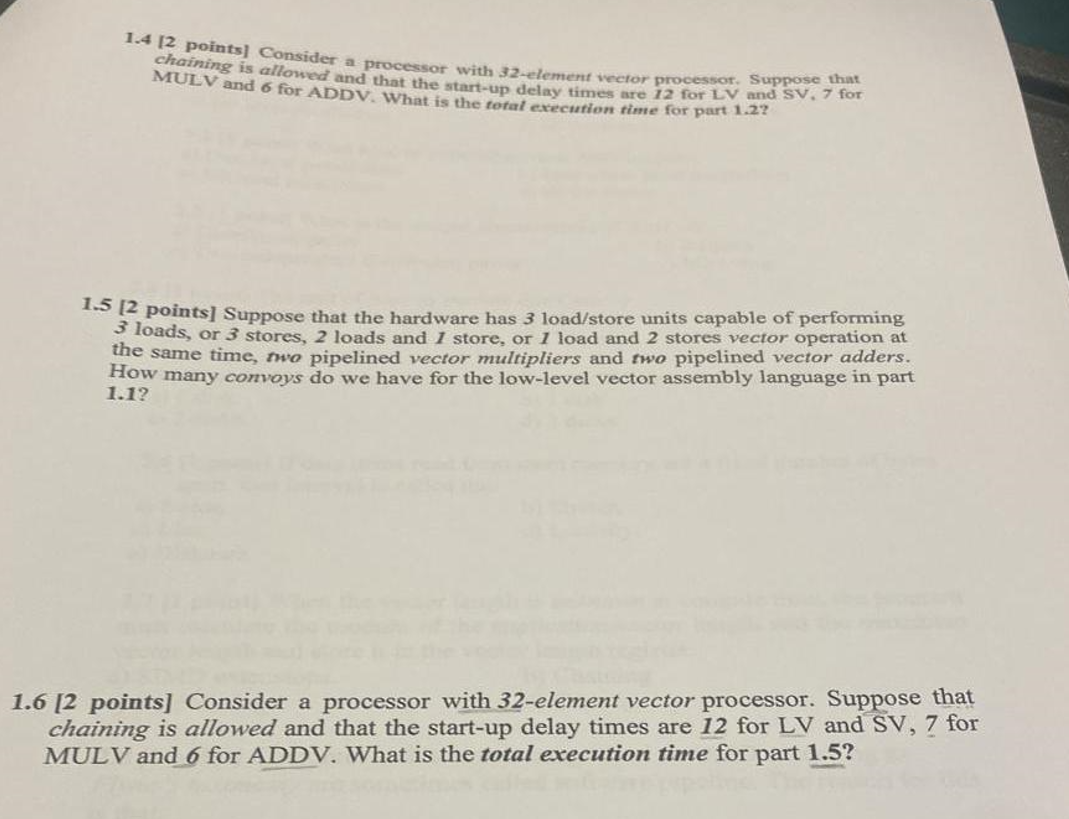

2 loads, or 2 stores, or 1 load and 1 store vector operation at the same time, one wipelined vector multiplier and one pipelined vector adder. 1.3 [2 points] Consider a processor with 32-element vector processor. Suppose that chaining is not allowed and that the start-up delay times are 12 for LV and SV, 7 for MULV and 6 for ADDV. What is the total execution time for part 1.2? 1.4 [2 points] Consider a processor with 32 -element wetor processor. Suppose that chaining is allowed and that the start-up delay times are 12 for LV and SV. 7 for MULV and 6 for ADDV. What is the torat execurion time for part 1.2? 1.5 [2 points] Suppose that the hardware has 310ad/ store units capable of performing 3 loads, or 3 stores, 2 loads and 1 store, or 1 load and 2 stores vector operation at the same time, mo pipelined vector multipliers and two pipelined vector adders. How many comvoys do we have for the low-level vector assembly language in part 1.1? 1.6 [2 points] Consider a processor with 32-element vector processor. Suppose that chaining is allowed and that the start-up delay times are 12 for LV and SV, 7 for MULV and 6 for ADDV. What is the total execution time for part 1.5 ? 2 loads, or 2 stores, or 1 load and 1 store vector operation at the same time, one wipelined vector multiplier and one pipelined vector adder. 1.3 [2 points] Consider a processor with 32-element vector processor. Suppose that chaining is not allowed and that the start-up delay times are 12 for LV and SV, 7 for MULV and 6 for ADDV. What is the total execution time for part 1.2? 1.4 [2 points] Consider a processor with 32 -element wetor processor. Suppose that chaining is allowed and that the start-up delay times are 12 for LV and SV. 7 for MULV and 6 for ADDV. What is the torat execurion time for part 1.2? 1.5 [2 points] Suppose that the hardware has 310ad/ store units capable of performing 3 loads, or 3 stores, 2 loads and 1 store, or 1 load and 2 stores vector operation at the same time, mo pipelined vector multipliers and two pipelined vector adders. How many comvoys do we have for the low-level vector assembly language in part 1.1? 1.6 [2 points] Consider a processor with 32-element vector processor. Suppose that chaining is allowed and that the start-up delay times are 12 for LV and SV, 7 for MULV and 6 for ADDV. What is the total execution time for part 1.5

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts