Question: 2. We have a computer that uses 32-bit addressing. Consider the scenario where a software process running on a 4-core processor has issued a memory

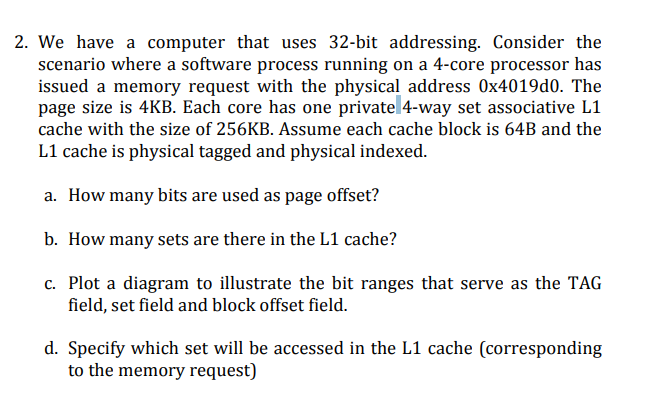

2. We have a computer that uses 32-bit addressing. Consider the scenario where a software process running on a 4-core processor has issued a memory request with the physical address 0x4019d0. The page size is 4KB. Each core has one private 4-way set associative L1 cache with the size of 256KB. Assume each cache block is 64B and the L1 cache is physical tagged and physical indexed. a. How many bits are used as page offset? b. How many sets are there in the L1 cache? c. Plot a diagram to illustrate the bit ranges that serve as the TAG field, set field and block offset field. d. Specify which set will be accessed in the L1 cache (corresponding to the memory request)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts