Question: 3. (15 points) Consider a virtual memory system with the following properties: 35-bit virtual address *16KB pages 33-bit physical address Assume that this virtual memory

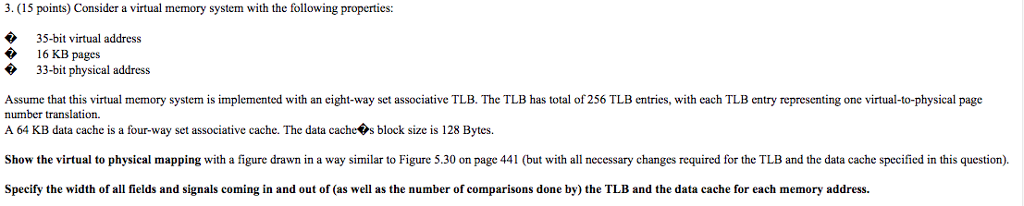

3. (15 points) Consider a virtual memory system with the following properties: 35-bit virtual address *16KB pages 33-bit physical address Assume that this virtual memory system is implemented with an eight-way set associative TLB. The TLB has total of 256 TLB entries, with each TLB entry representing one virtual-to-physical page number translation A 64 KB data cache is a four-way set associative cache. The data cache+s block size is 128 Bytes. Show the virtual to physical mapping with a figure drawn in a way similar to Figure 5.30 on page 441 (but with all necessary changes required for the TLB and the data cache specified in this question). Specify the width of all fields and signals coming in and out of (as well as the number of comparisons done by) the TLB and the data cache for each memory address. 3. (15 points) Consider a virtual memory system with the following properties: 35-bit virtual address *16KB pages 33-bit physical address Assume that this virtual memory system is implemented with an eight-way set associative TLB. The TLB has total of 256 TLB entries, with each TLB entry representing one virtual-to-physical page number translation A 64 KB data cache is a four-way set associative cache. The data cache+s block size is 128 Bytes. Show the virtual to physical mapping with a figure drawn in a way similar to Figure 5.30 on page 441 (but with all necessary changes required for the TLB and the data cache specified in this question). Specify the width of all fields and signals coming in and out of (as well as the number of comparisons done by) the TLB and the data cache for each memory address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts