Question: 3 ) A DRAM chip utilizes a 1 T - 1 C ( one transistor and one capacitor ) configuration. The capacitance of each DRAM

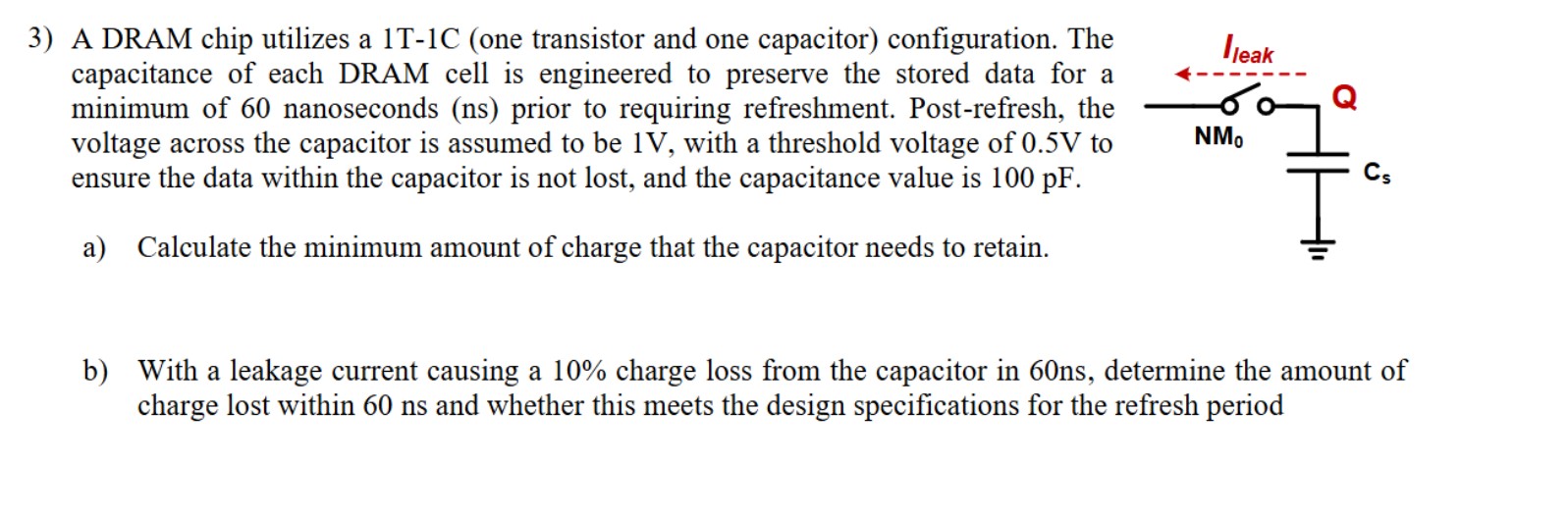

A DRAM chip utilizes a TC one transistor and one capacitor configuration. The capacitance of each DRAM cell is engineered to preserve the stored data for a minimum of nanoseconds ns prior to requiring refreshment. Postrefresh, the voltage across the capacitor is assumed to be V with a threshold voltage of V to ensure the data within the capacitor is not lost, and the capacitance value is pF

a Calculate the minimum amount of charge that the capacitor needs to retain.

b With a leakage current causing a charge loss from the capacitor in ns determine the amount of charge lost within ns and whether this meets the design specifications for the refresh period

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock