Question: 3. Consider the MIPS code below: addi $t0,$t1,1 sub $t1,$so, $s1 add $81,$t0,$t1 xor $t0,$t1,$s1 (a) Assume that we execute the code on a superscalar

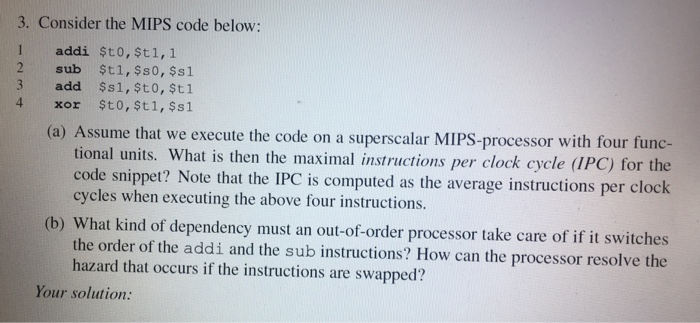

3. Consider the MIPS code below: addi $t0,$t1,1 sub $t1,$so, $s1 add $81,$t0,$t1 xor $t0,$t1,$s1 (a) Assume that we execute the code on a superscalar MIPS-processor with four func- tional units. What is then the maximal instructions per clock cycle (IPC) for the code snippet? Note that the IPC is computed as the average instructions per clock cycles when executing the above four instructions. (b) What kind of dependency must an out-of-order processor take care of if it switches the order of the addi and the sub instructions? How can the processor resolve the hazard that occurs if the instructions are swapped? Your solution: 3. Consider the MIPS code below: addi $t0,$t1,1 sub $t1,$so, $s1 add $81,$t0,$t1 xor $t0,$t1,$s1 (a) Assume that we execute the code on a superscalar MIPS-processor with four func- tional units. What is then the maximal instructions per clock cycle (IPC) for the code snippet? Note that the IPC is computed as the average instructions per clock cycles when executing the above four instructions. (b) What kind of dependency must an out-of-order processor take care of if it switches the order of the addi and the sub instructions? How can the processor resolve the hazard that occurs if the instructions are swapped? Your solution

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts